11-14 Vol. 3

MEMORY CACHE CONTROL

The L1 instruction cache in P6 family processors implements only the “SI” part of the

MESI protocol, because the instruction cache is not writable. The instruction cache

monitors changes in the data cache to maintain consistency between the caches

when instructions are modified. See

Section 11.6, “Self-Modifying Code,” for more

information on the implications of caching instructions.

11.5 CACHE CONTROL

The Intel 64 and IA-32 architectures provide a variety of mechanisms for controlling

the caching of data and instructions and for controlling the ordering of reads and

writes between the processor, the caches, and memory. These mechanisms can be

divided into two groups:

• Cache control registers and bits — The Intel 64 and IA-32 architectures

define several dedicated registers and various bits within control registers and

page- and directory-table entries that control the caching system memory

locations in the L1, L2, and L3 caches. These mechanisms control the caching of

virtual memory pages and of regions of physical memory.

• Cache control and memory ordering instructions — The Intel 64 and IA-32

architectures provide several instructions that control the caching of data, the

ordering of memory reads and writes, and the prefetching of data. These instruc

-

tions allow software to control the caching of specific data structures, to control

memory coherency for specific locations in memory, and to force strong memory

ordering at specific locations in a program.

The following sections describe these two groups of cache control mechanisms.

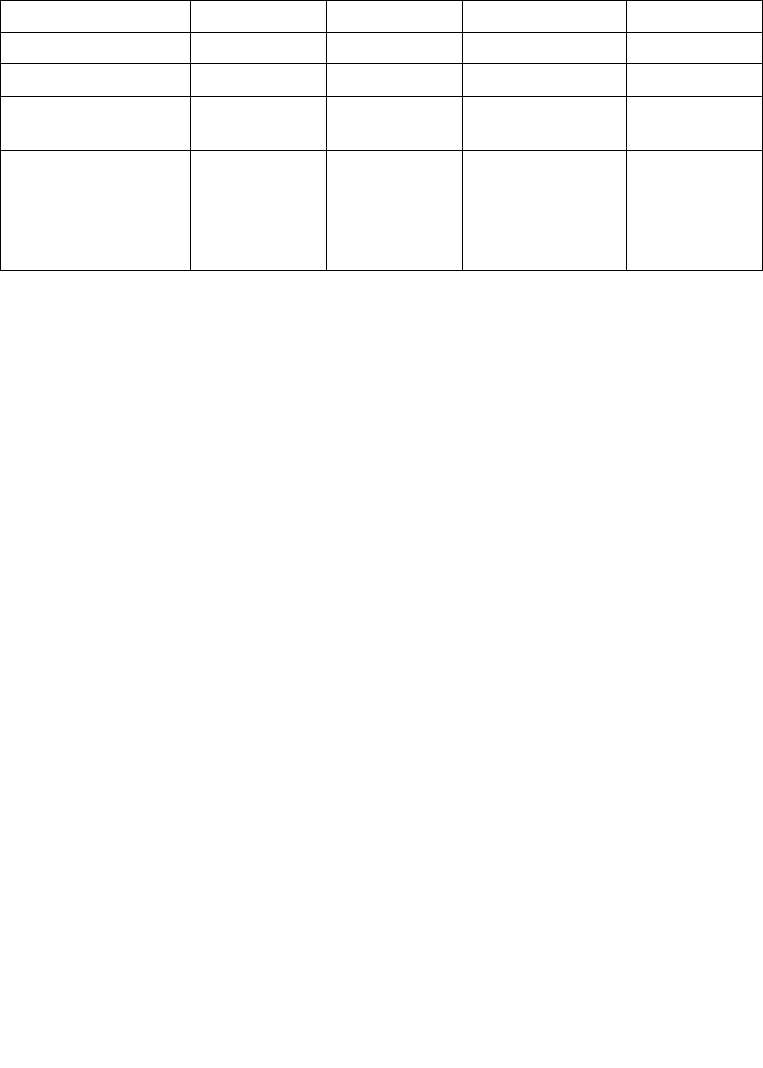

Table 11-4. MESI Cache Line States

Cache Line State M (Modified) E (Exclusive) S (Shared) I (Invalid)

This cache line is valid? Yes Yes Yes No

The memory copy is… Out of date Valid Valid —

Copies exist in caches

of other processors?

No No Maybe Maybe

A write to this line … Does not go to

the system bus.

Does not go to

the system bus.

Causes the

processor to gain

exclusive

ownership of the

line.

Goes directly to

the system bus.