16-40 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

Additional information is saved if an exception or interrupt occurs in conjunction with

a branch instruction. If a branch instruction generates a trap type exception, two

branch records are stored in the LBR stack: a branch record for the branch instruction

followed by a branch record for the exception.

If a branch instruction is immediately followed by an interrupt, a branch record is

stored in the LBR stack for the branch instruction followed by a record for the

interrupt.

16.7.3 Last Exception Records

The Pentium 4, Intel Xeon, Pentium M, Intel

®

Core™ Solo, Intel

®

Core™ Duo, Intel

®

Core™2 Duo, Intel

®

Core™ i7 and Intel

®

Atom™ processors provide two MSRs (the

MSR_LER_TO_LIP and the MSR_LER_FROM_LIP MSRs) that duplicate the functions

of the LastExceptionToIP and LastExceptionFromIP MSRs found in the P6 family

processors. The MSR_LER_TO_LIP and MSR_LER_FROM_LIP MSRs contain a branch

record for the last branch that the processor took prior to an exception or interrupt

being generated.

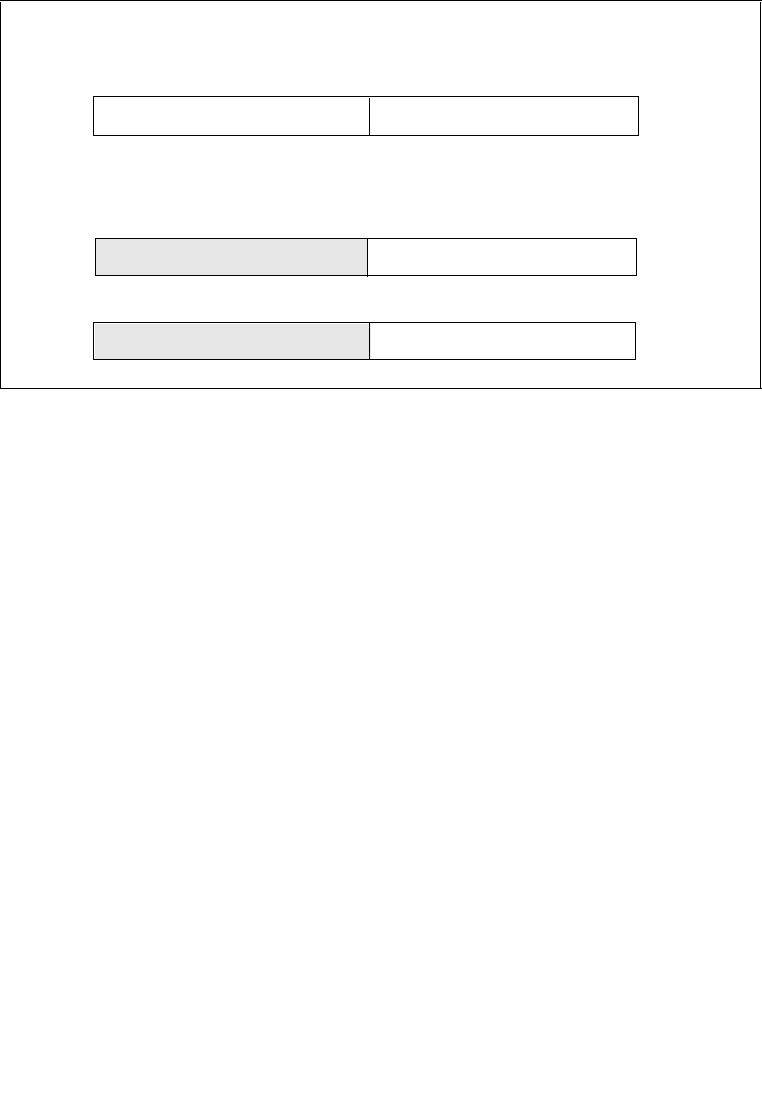

Figure 16-13. LBR MSR Branch Record Layout for the Pentium 4

and Intel Xeon Processor Family

63

From Linear Address

0

To Linear Address

63

From Linear Address

0

0

63

To Linear Address

32 - 31

MSR_LASTBRANCH_0 through MSR_LASTBRANCH_3

CPUID Family 0FH, Models 0H-02H

Reserved

CPUID Family 0FH, Model 03H-04H

Reserved

MSR_LASTBRANCH_0_FROM_LIP through MSR_LASTBRANCH_15_FROM_LIP

32 - 31

32 - 31

MSR_LASTBRANCH_0_TO_LIP through MSR_LASTBRANCH_15_TO_LIP