Vol. 3 12-7

INTEL

®

MMX

™

TECHNOLOGY SYSTEM PROGRAMMING

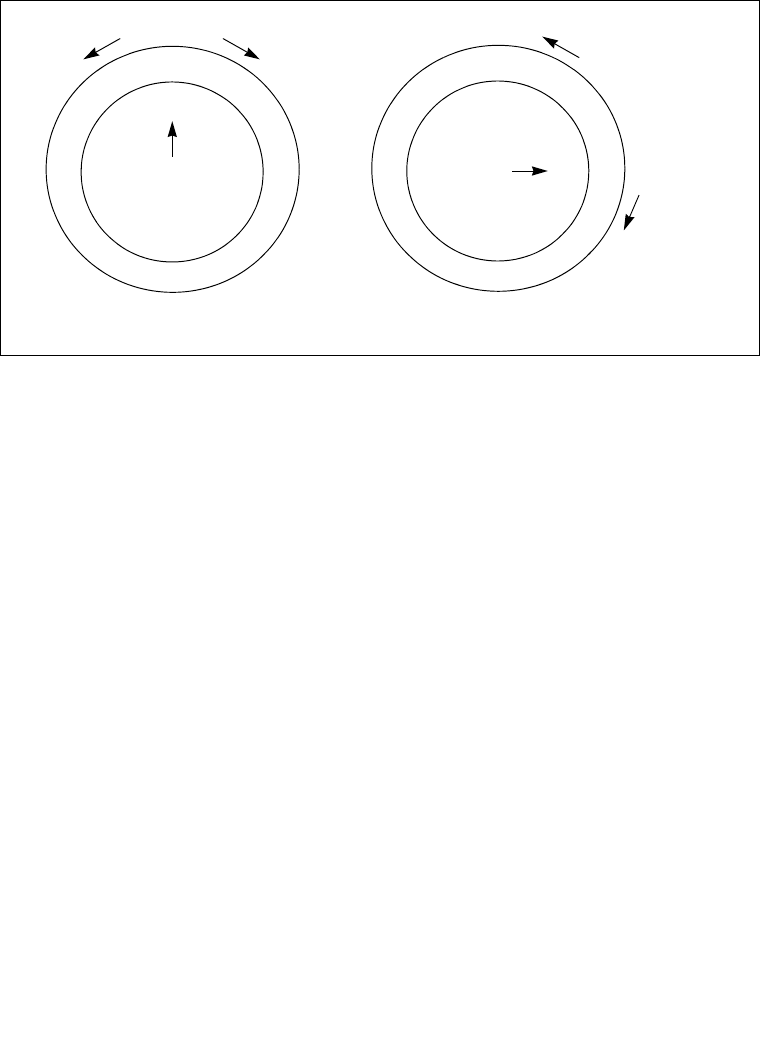

When the TOS equals 2 (case B in Figure 12-2), ST0 points to the physical location

R2. MM0 maps to ST6, MM1 maps to ST7, MM2 maps to ST0, and so on.

Figure 12-2. Mapping of MMX Registers to x87 FPU Data Register Stack

MM0

MM1

MM2

MM3

MM4

MM5

MM6

MM7

ST1

ST2

ST7

ST0

ST6

ST7

ST1

TOS

TOS

x87 FPU “push”

x87 FPU “pop”

x87 FPU “push”

x87 FPU “pop”

Case A: TOS=0

Case B: TOS=2

MM0

MM1

MM2

MM3

MM4

MM5

MM6

MM7

ST0

Outer circle = x87 FPU data register’s logical location relative to TOS

Inner circle = x87 FPU tags = MMX register’s location = FP registers’s physical location

(R0)

(R2)

(R2)

(R0)