Vol. 3 16-35

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

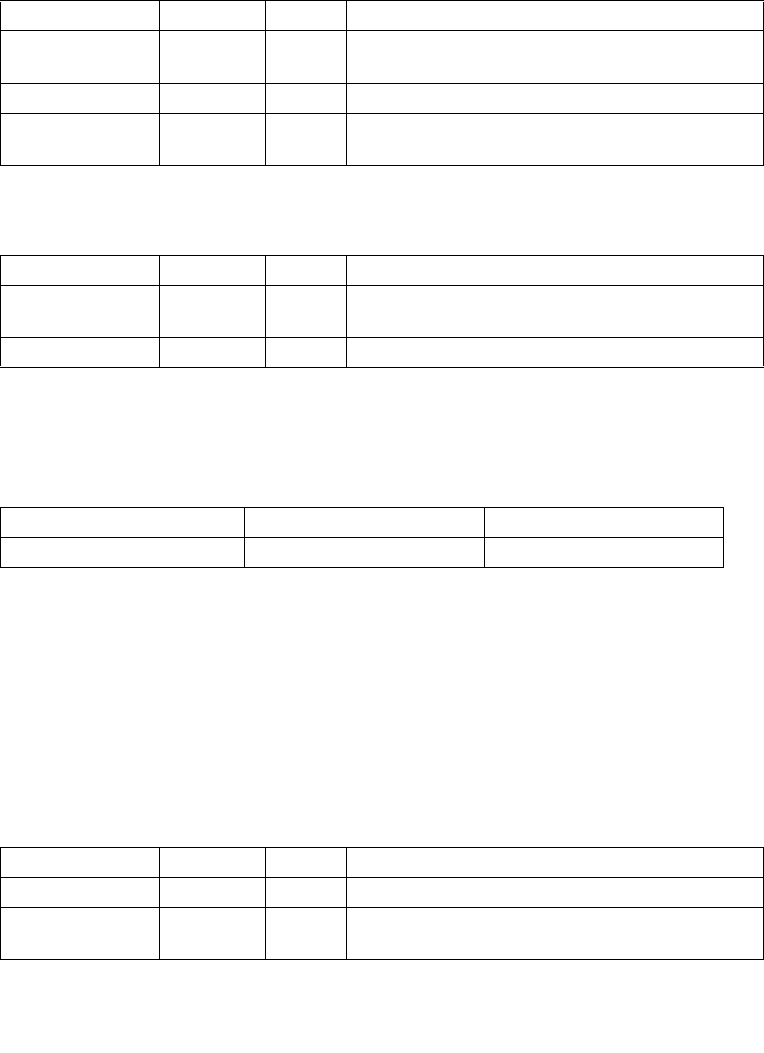

Processors based on Intel microarchitecture (Nehalem) have an LBR MSR Stack as

shown in Table 16-8.

Table 16-8. LBR Stack Size and TOS Pointer Range

16.6.2 Filtering of Last Branch Records

MSR_LBR_SELECT is cleared to zero at RESET, and LBR filtering is disabled, i.e. all

branches will be captured. MSR_LBR_SELECT provides bit fields to specify the condi-

tions of subsets of branches that will not be captured in the LBR. The layout of

MSR_LBR_SELECT is shown in Table 16-9.

Table 16-6. IA32_LASTBRACH_x_FROM_IP

Bit Field Bit Offset Access Description

Data 47:0 R/O The linear address of the branch instruction itself,

This is the “branch from“ address

SIGN_EXt 62:48 R/0 Signed extension of bit 47 of this register

MISPRED 63 R/O When set, indicates the branch was predicted;

otherwise, the branch was mispredicted.

Table 16-7. IA32_LASTBRACH_x_TO_IP

Bit Field Bit Offset Access Description

Data 47:0 R/O The linear address of the target of the branch

instruction itself, This is the “branch to“ address

SIGN_EXt 63:48 R/0 Signed extension of bit 47 of this register

DisplayFamily_DisplayModel Size of LBR Stack Range of TOS Pointer

06_1AH 16 0 to 15

Table 16-9. MSR_LBR_SELECT

Bit Field Bit Offset Access Description

CPL_EQ_0 0 R/W When set, do not capture branches occurring in ring 0

CPL_NEQ_0 1 R/W When set, do not capture branches occurring in ring

>0