15-30 Vol. 3

MACHINE-CHECK ARCHITECTURE

also write a 16-bit model-specific error code in the IA32_MCi_STATUS

register depending on the implementation of the machine-check architec

-

ture of the processor.

The MCA error codes are architecturally defined for Intel 64 and IA-32

processors. To determine the cause of a machine-check exception, the

machine-check exception handler must read the VAL flag for each

IA32_MCi_STATUS register. If the flag is set, the machine check-exception

handler must then read the MCA error code field of the register. It is the

encoding of the MCA error code field [15:0] that determines the type of error

being reported and not the register bank reporting it.

There are two types of MCA error codes: simple error codes and compound

error codes.

15.9.1 Simple Error Codes

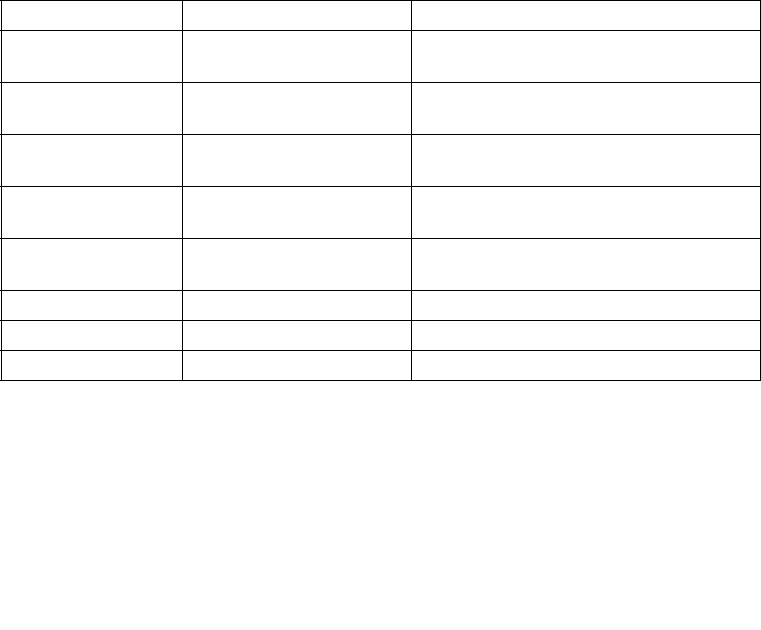

Table 15-8 shows the simple error codes. These unique codes indicate global

error information.

Table 15-8. IA32_MCi_Status [15:0] Simple Error Code Encoding

Error Code Binary Encoding Meaning

No Error 0000 0000 0000 0000 No error has been reported to this bank of

error-reporting registers.

Unclassified 0000 0000 0000 0001 This error has not been classified into the

MCA error classes.

Microcode ROM Parity

Error

0000 0000 0000 0010 Parity error in internal microcode ROM

External Error 0000 0000 0000 0011 The BINIT# from another processor caused

this processor to enter machine check.

1

FRC Error 0000 0000 0000 0100 FRC (functional redundancy check)

master/slave error

Internal Parity Error 0000 0000 0000 0101 Internal parity error.

Internal Timer Error 0000 0100 0000 0000 Internal timer error.

Internal Unclassified 0000 01xx xxxx xxxx Internal unclassified errors.

2

NOTES:

1. BINIT# assertion will cause a machine check exception if the processor (or any processor on the

same external bus) has BINIT# observation enabled during power-on configuration (hardware

strapping) and if machine check exceptions are enabled (by setting CR4.MCE = 1).

2. At least one X must equal one. Internal unclassified errors have not been classified.