15-8 Vol. 3

MACHINE-CHECK ARCHITECTURE

introduced with Intel 64 processor having CPUID

DisplayFamily_DisplayModel encoding of 06H_1AH.

Where:

• MCA (machine-check architecture) error code field, bits 15:0 — Specifies

the machine-check architecture-defined error code for the machine-check error

condition detected. The machine-check architecture-defined error codes are

guaranteed to be the same for all IA-32 processors that implement the machine-

check architecture. See

Section 15.9, “Interpreting the MCA Error Codes,” and

Appendix E, “Interpreting Machine-Check Error Codes”, for information on

machine-check error codes.

• Model-specific error code field, bits 31:16 — Specifies the model-specific

error code that uniquely identifies the machine-check error condition detected.

The model-specific error codes may differ among IA-32 processors for the same

machine-check error condition. See

Appendix E, “Interpreting Machine-Check

Error Codes”for information on model-specific error codes.

• Reserved, Error Status, and Other Information fields, bits 56:32 —

• Bits 37:32 always contain “Other Information” that is implementation-

specific and is not part of the machine-check architecture. Software that

is intended to be portable among IA-32 processors should not rely on

these values.

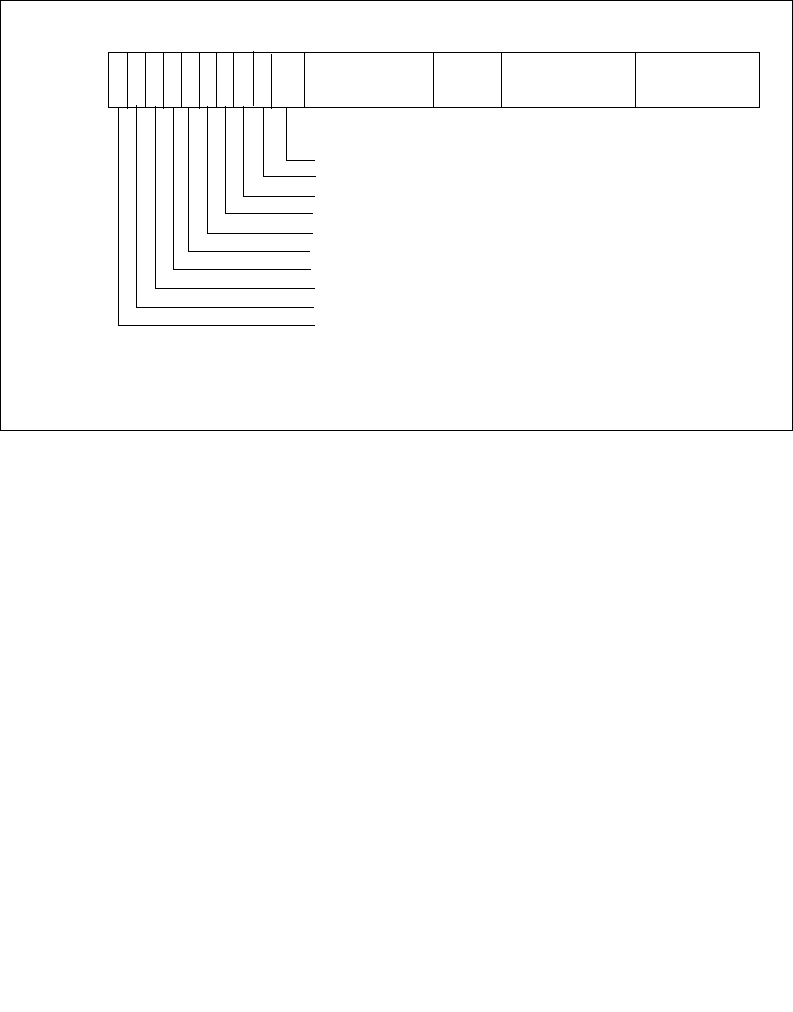

Figure 15-5. IA32_MCi_STATUS Register

63

Threshold-based error status (54:53)*

AR — Recovery action required for UCR error (55)**

S — Signaling an uncorrected recoverable (UCR) error (56)**

PCC — Processor context corrupted (57)

37 32 31 16

0

P

C

A

E

ADDRV — MCi_ADDR register valid (58)

MISCV — MCi_MISC register valid (59)

EN — Error reporting enabled (60)

UC — Uncorrected error (61)

OVER — Error overflow (62)

VAL — MCi_STATUS register valid (63)

C

MCA Error Code

U

S

R

Other

MSCOD Model

5453 386261605958575655 52 15

V

A

L

O

V

E

R

C

N

Specific Error Code

Info

Corrected Error

Count

* When IA32_MCG_CAP[11] (MCG_TES_P) is not set, these bits are model-specific

(part of “Other Information”).

** When IA32_MCG_CAP[11] or IA32_MCG_CAP[24] are not set, these bits are reserved, or

model-specific (part of “Other Information”).