Vol. 3 13-19

SYSTEM PROGRAMMING FOR INSTRUCTION SET EXTENSIONS AND

If all three requirements are met, applications can use the target new instruction set

extensions. If any of the above requirements are not met, an attempt to execute an

instruction operating on a processor extended state corresponding to bit offset

higher than 1 in the XFEATURE_ENABLED_MASK register (XCR0) will cause a #UD

exception.

Newer instruction extensions operating on SSE state, but not on any processor

extended states corresponding bits in XCR0 with an offset higher than 1, follow the

programming model described by

Section 13.1 through Section 13.5. XCR0 is not

required to enable OS support for SSE state management, but CR4.OSFXSR is

required.

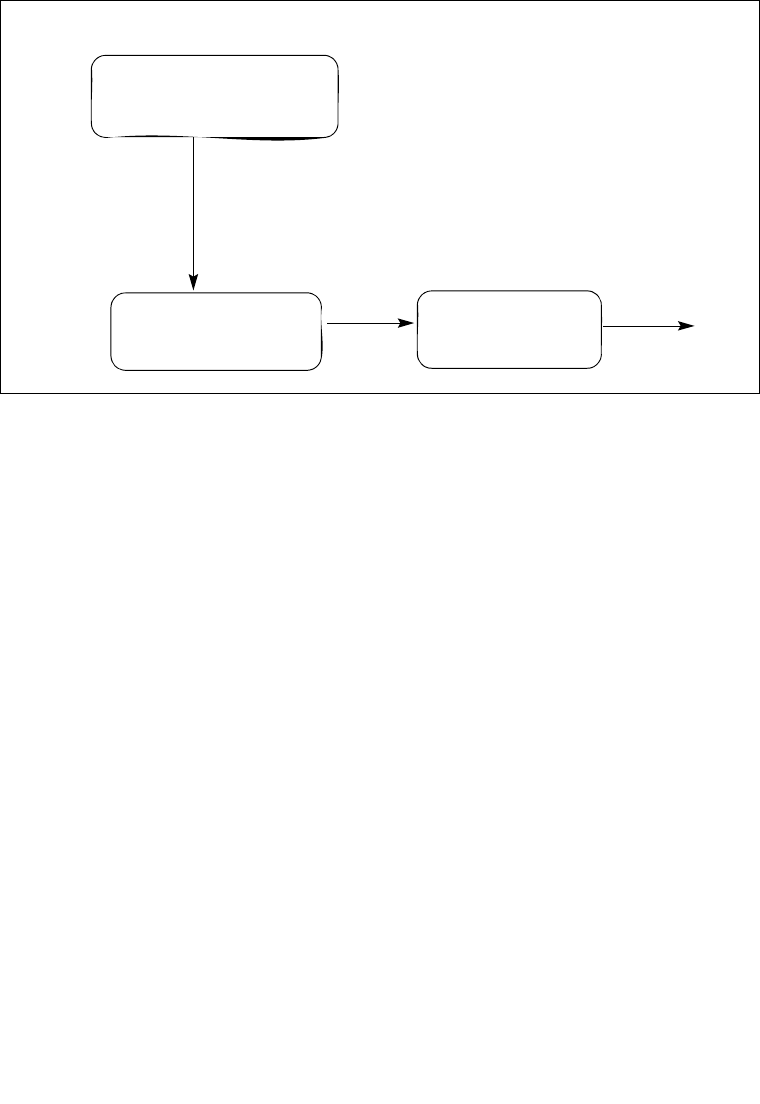

Figure 13-4. Application Detection of New Instruction Extensions and Processor

Extended State

Implied HW support for

Check enabled state in

XCR0 via XGETBV

Check feature flag

for Instruction set

Check feature flag

CPUID.1H:ECX.OXSAVE = 1?

OS provides processor

extended state management

State

ok to use

XSAVE, XRSTOR, XGETBV, XCR0

enabled

Instructions

Yes