10-24 Vol. 3

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

The default value for SVR[bit 12] is clear, indicating that an EOI broadcast will be

performed.

The support for Directed EOI capability can be detected by means of bit 24 in the

Local APIC Version Register. This feature is supported in both the xAPIC mode and

x2APIC modes of a local x2APIC unit. Layout of the Local APIC Version register is as

shown in

Figure 10-10. The Directed EOI feature is supported if bit 24 is set to 1.

10.5.6 x2APIC State Transitions

This section provides a detailed description of the x2APIC states of a local x2APIC

unit, transitions between these states as well as interactions of these states with INIT

and RESET.

10.5.6.1 x2APIC States

The valid states for a local x2APIC unit is listed in Table 10-2:

• APIC disabled: IA32_APIC_BASE[EN]=0 and IA32_APIC_BASE[EXTD]=0

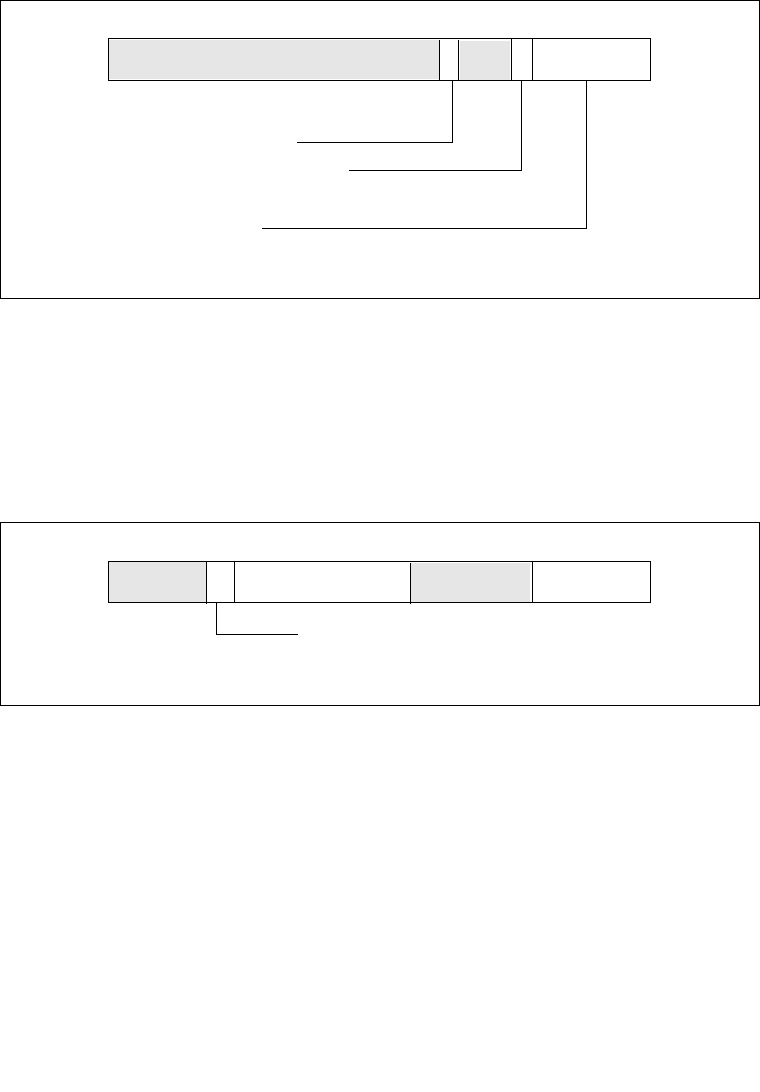

Figure 10-9. Spurious Interrupt Vector Register (SVR) of x2APIC

Figure 10-10. Local APIC Version Register of x2APIC

31

0

Reserved

7

APIC Software Enable/Disable

8911

0: APIC Disabled

1: APIC Enabled

Spurious Vector

MMIO Address: FEE0 00F0H

MSR Address: 080FH

EOI Broadcast Disable

12

31

0

Reserved

78

23 15

MMIO Address: FEE0 0030H

MSR Address: 0803H

Directed EOI Support

16

Reserved

25

24

Vector

Max LVT Entry