4-18 Vol. 3

PAGING

processor ignores bits 63:1, and there is no mapping for the 1-GByte region

controlled by PDPTEi. A reference using a linear address in this region causes a

page-fault exception (see Section 4.7).

• If the P flag of PDPTEi is 1, 4-KByte naturally aligned page directory is located at

the physical address specified in bits 51:12 of PDPTEi (see Table 4-8 in Section

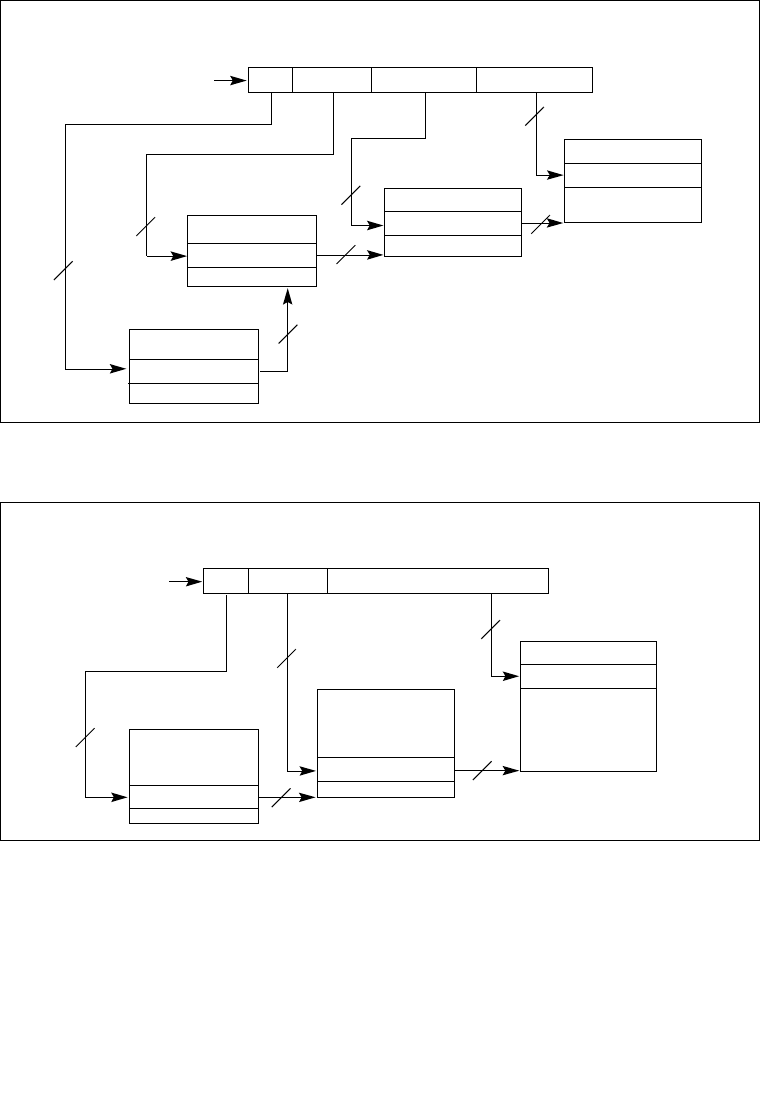

Figure 4-5. Linear-Address Translation to a 4-KByte Page using PAE Paging

Figure 4-6. Linear-Address Translation to a 2-MByte Page using PAE Paging

0

Directory

Table

Offset

Page Directory

PDE with PS=0

Page Table

PTE

4-KByte Page

Physical Address

31 20 111221

Linear Address

PDPTE value

30 29

PDPTE Registers

Directory Pointer

2

9

12

9

40

40

40

0

Directory

Offset

Page Directory

PDE with PS=1

2-MByte Page

Physical Address

31 2021

Linear Address

PDPTE value

30 29

PDPTE Registers

Directory

Pointer

2

9

21

31

40