9-2 Vol. 3

PROCESSOR MANAGEMENT AND INITIALIZATION

The software-initialization code performs all system-specific initialization of the BSP

or primary processor and the system logic.

At this point, for MP (or DP) systems, the BSP (or primary) processor wakes up each

AP (or secondary) processor to enable those processors to execute self-configuration

code.

When all processors are initialized, configured, and synchronized, the BSP or primary

processor begins executing an initial operating-system or executive task.

The x87 FPU is also initialized to a known state during hardware reset. x87 FPU soft-

ware initialization code can then be executed to perform operations such as setting

the precision of the x87 FPU and the exception masks. No special initialization of the

x87 FPU is required to switch operating modes.

Asserting the INIT# pin on the processor invokes a similar response to a hardware

reset. The major difference is that during an INIT, the internal caches, MSRs, MTRRs,

and x87 FPU state are left unchanged (although, the TLBs and BTB are invalidated as

with a hardware reset). An INIT provides a method for switching from protected to

real-address mode while maintaining the contents of the internal caches.

9.1.1 Processor State After Reset

Table 9-1 shows the state of the flags and other registers following power-up for the

Pentium 4, Intel Xeon, P6 family, and Pentium processors. The state of control

register CR0 is 60000010H (see Figure 9-1). This places the processor is in real-

address mode with paging disabled.

9.1.2 Processor Built-In Self-Test (BIST)

Hardware may request that the BIST be performed at power-up. The EAX register is

cleared (0H) if the processor passes the BIST. A nonzero value in the EAX register

after the BIST indicates that a processor fault was detected. If the BIST is not

requested, the contents of the EAX register after a hardware reset is 0H.

The overhead for performing a BIST varies between processor families. For example,

the BIST takes approximately 30 million processor clock periods to execute on the

Pentium 4 processor. This clock count is model-specific; Intel reserves the right to

change the number of periods for any Intel 64 or IA-32 processor, without notification.

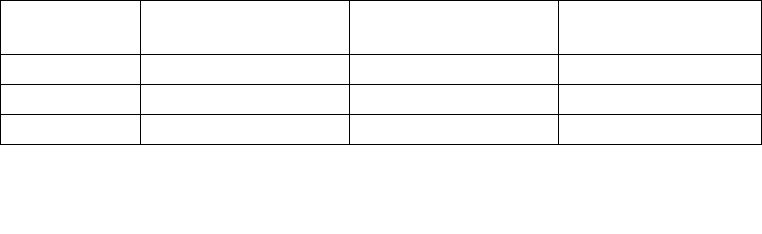

Table 9-1. IA-32 Processor States Following Power-up, Reset, or INIT

Register Pentium 4 and Intel

Xeon Processor

P6 Family Processor Pentium Processor

EFLAGS

1

00000002H 00000002H 00000002H

EIP 0000FFF0H 0000FFF0H 0000FFF0H

CR0 60000010H

2

60000010H

2

60000010H

2