Vol. 3 13-17

SYSTEM PROGRAMMING FOR INSTRUCTION SET EXTENSIONS AND

13.8 DETECTION, ENUMERATION, ENABLING PROCESSOR

EXTENDED STATE SUPPORT

An OS can determine if the XSAVE/XRSTOR/XGETBV/XSETBV instructions and the

XFEATURE_ENABLED_MASK register (XCR0) are available in the processor by

checking the value of CPUID.1.ECX.XSAVE to be 1. The OS must set CR4.OSXSAVE to

1 to enable the new instructions. The OS uses XSETBV to enable the processor state

component (setting the corresponding bit in XCR0 to 1) that it will manage using

XSAVE/XRSTOR. Bit 0 of XCR0 must be set to 1. The value of CR4.OSXSAVE is

reflected in CPUID.01H:ECX.OSXSAVE (bit 27) to communicate the setting to non-

privileged software.

The bits that must be enabled in the XFEATURE_ENABLED_MASK register (XCR0)

and the size of the memory region needed to save processor extended state informa

-

tion must be enumerated by CPUID leaf 0DH with ECX = 0 as input. However, the

recommended usage by system software to use XSAVE/XRSTOR is to:

• Allocate a memory buffer according to the size reported by CPUID.(EAX=0DH,

ECX=0H):ECX. The value reported by CPUID.(EAX=0DH, ECX=0H):ECX always

includes the size of the header. Clear the entire buffer prior to being used by

XSAVE.

• Provide EDX:EAX with all bits set to 1 for XSAVE and XRSTOR instructions.

An alternative approach is to read the master bit vector mask EDX:EAX reported by

CPUID.(EAX=0D, ECX=0H). This mask may be used as input to the XSAVE/XRSTOR

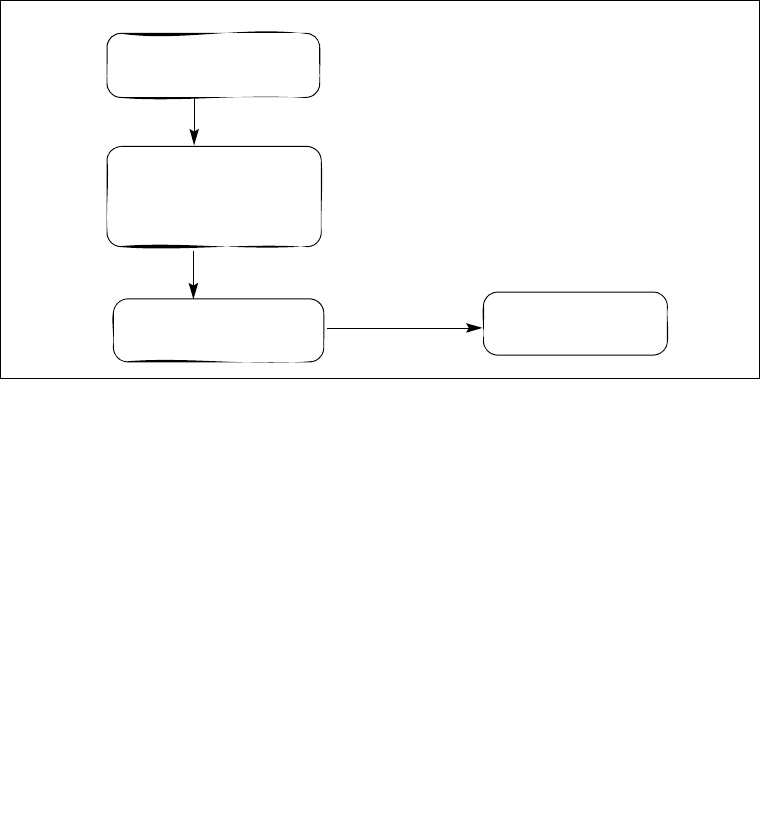

Figure 13-3. OS Enabling of Processor Extended State Support

Check

HW support XSAVE, XRSTOR, XSETBV, XFEM

CPUID.1H:ECX.XSAVE?

Enumerate

Extended state features

Buffer size requirement

Set valid bits in

XCR0 via XSETBV

Set CR4.OSXSAVE

to 1

Clear buffer to 0

XSETBV enabled