16-10 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

See also: Chapter 6, “Interrupt 1—Debug Exception (#DB),” in the Intel® 64 and

IA-32 Architectures Software Developer’s Manual, Volume 3A.

16.3.1.1 Instruction-Breakpoint Exception Condition

The processor reports an instruction breakpoint when it attempts to execute an

instruction at an address specified in a breakpoint-address register (DB0 through

DR3) that has been set up to detect instruction execution (R/W flag is set to 0). Upon

reporting the instruction breakpoint, the processor generates a fault-class, debug

exception (#DB) before it executes the target instruction for the breakpoint.

Instruction breakpoints are the highest priority debug exceptions. They are serviced

before any other exceptions detected during the decoding or execution of an instruc-

tion. However, if a code instruction breakpoint is placed on an instruction located

immediately after a POP SS/MOV SS instruction, the breakpoint may not be trig-

gered. In most situations, POP SS/MOV SS will inhibit such interrupts (see

“MOV—Move” and “POP—Pop a Value from the Stack” in Chapters 3 and 4 of the

Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volumes

2A & 2B).

Because the debug exception for an instruction breakpoint is generated before the

instruction is executed, if the instruction breakpoint is not removed by the exception

handler; the processor will detect the instruction breakpoint again when the instruc-

tion is restarted and generate another debug exception. To prevent looping on an

instruction breakpoint, the Intel 64 and IA-32 architectures provide the RF flag

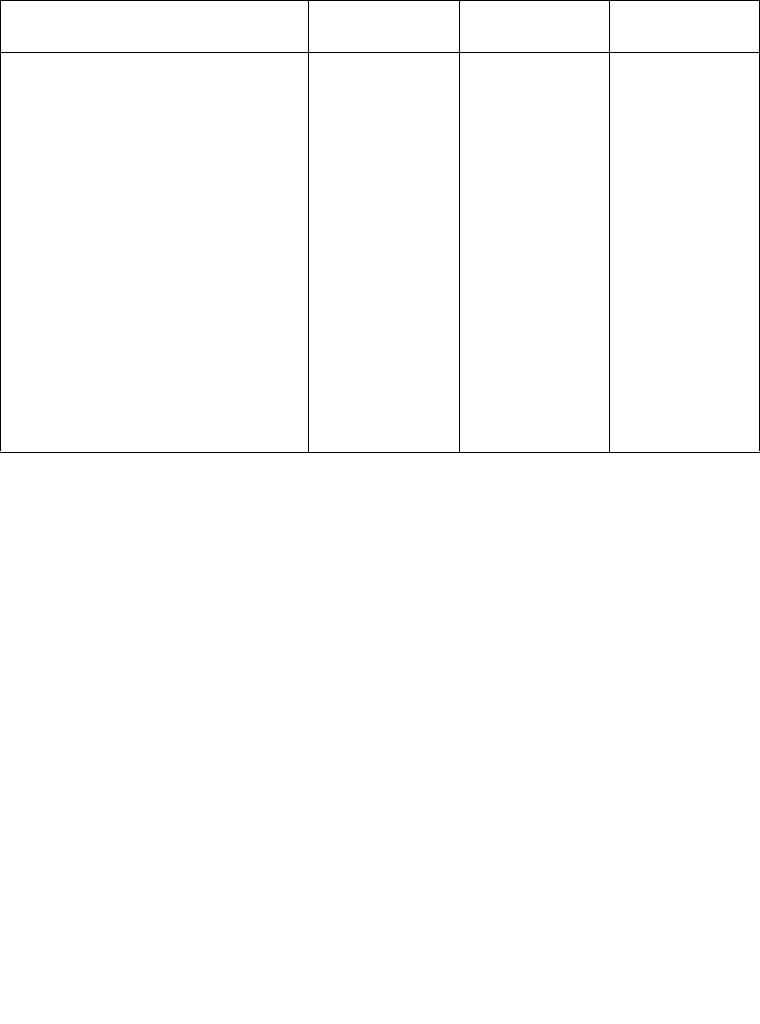

Table 16-2. Debug Exception Conditions

Debug or Breakpoint Condition DR6 Flags

Tested

DR7 Flags

Tested

Exception Class

Single-step trap BS = 1 Trap

Instruction breakpoint, at addresses

defined by DRn and LENn

Bn = 1 and

(Gn or Ln = 1)

R/Wn = 0 Fault

Data write breakpoint, at addresses

defined by DRn and LENn

Bn = 1 and

(Gn or Ln = 1)

R/Wn = 1 Trap

I/O read or write breakpoint, at

addresses defined by DRn and LENn

Bn = 1 and

(Gn or Ln = 1)

R/Wn = 2 Trap

Data read or write (but not instruction

fetches), at addresses defined by DRn

and LENn

Bn = 1 and

(Gn or Ln = 1)

R/Wn = 3 Trap

General detect fault, resulting from an

attempt to modify debug registers

(usually in conjunction with in-circuit

emulation)

BD = 1 Fault

Task switch BT = 1 Trap