Vol. 3 10-45

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

ICR in xAPIC mode, except the Delivery Status bit is removed since it is not needed

in x2APIC mode. The destination ID field is expanded to 32 bits in x2APIC mode.

To send an IPI, software must set up the ICR or SELF IPI register to indicate the type

of IPI message to be sent and the destination processor or processors.

A single MSR write to the Interrupt Command Register is required for dispatching an

interrupt in x2APIC mode. With the removal of the Delivery Status bit, system soft

-

ware no longer has a reason to read the ICR. It remains readable only to aid in

debugging.

A destination ID value of FFFF_FFFFH is used for broadcast of interrupts in both

logical destination and physical destination modes.

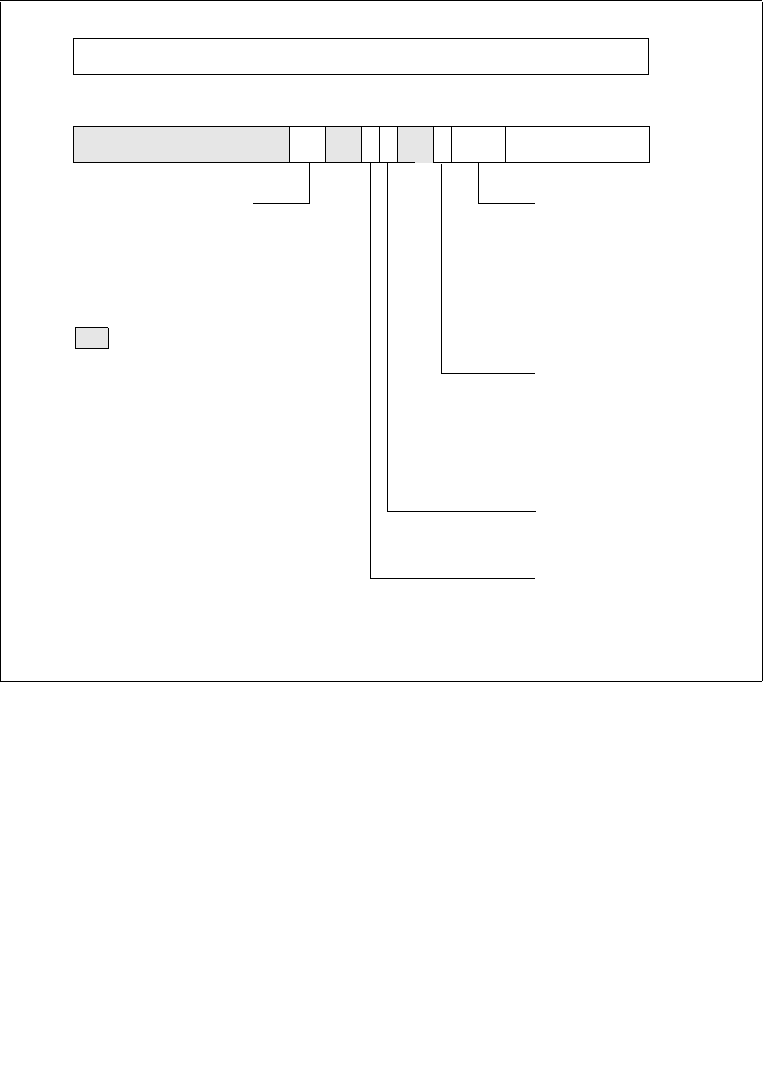

Figure 10-18. Interrupt Command Register (ICR) in x2APIC Mode

31 0

Reserved

7

Vector

Destination Shorthand

810

Delivery Mode

000: Fixed

001: Reserved

00: No Shorthand

01: Self

111213141516171819

10: All Including Self

11: All Excluding Self

010: SMI

011: Reserved

100: NMI

101: INIT

110: Start Up

111: Reserved

Destination Mode

0: Physical

1: Logical

Level

0 = De-assert

1 = Assert

Trigger Mode

0: Edge

1: Level

63

32

Destination Field

Address: 830H (63 - 0)

Value after Reset: 0H

Reserved

20