16-38 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

• BTS (branch trace store) flag (bit 3) — When set, enables the BTS facilities to

log BTMs to a memory-resident BTS buffer that is part of the DS save area. See

Section 16.4.9, “BTS and DS Save Area.”

• BTINT (branch trace interrupt) flag (bits 4) — When set, the BTS facilities

generate an interrupt when the BTS buffer is full. When clear, BTMs are logged to

the BTS buffer in a circular fashion. See Section 16.4.5, “Branch Trace Store (BTS).”

• BTS_OFF_OS (disable ring 0 branch trace store) flag (bit 5) — When set,

enables the BTS facilities to skip sending/logging CPL_0 BTMs to the memory-

resident BTS buffer. See Section 16.7.2, “LBR Stack for Processors Based on Intel

NetBurst Microarchitecture.”

• BTS_OFF_USR (disable ring 0 branch trace store) flag (bit 6) — When set,

enables the BTS facilities to skip sending/logging non-CPL_0 BTMs to the

memory-resident BTS buffer. See Section 16.7.2, “LBR Stack for Processors

Based on Intel NetBurst Microarchitecture.”

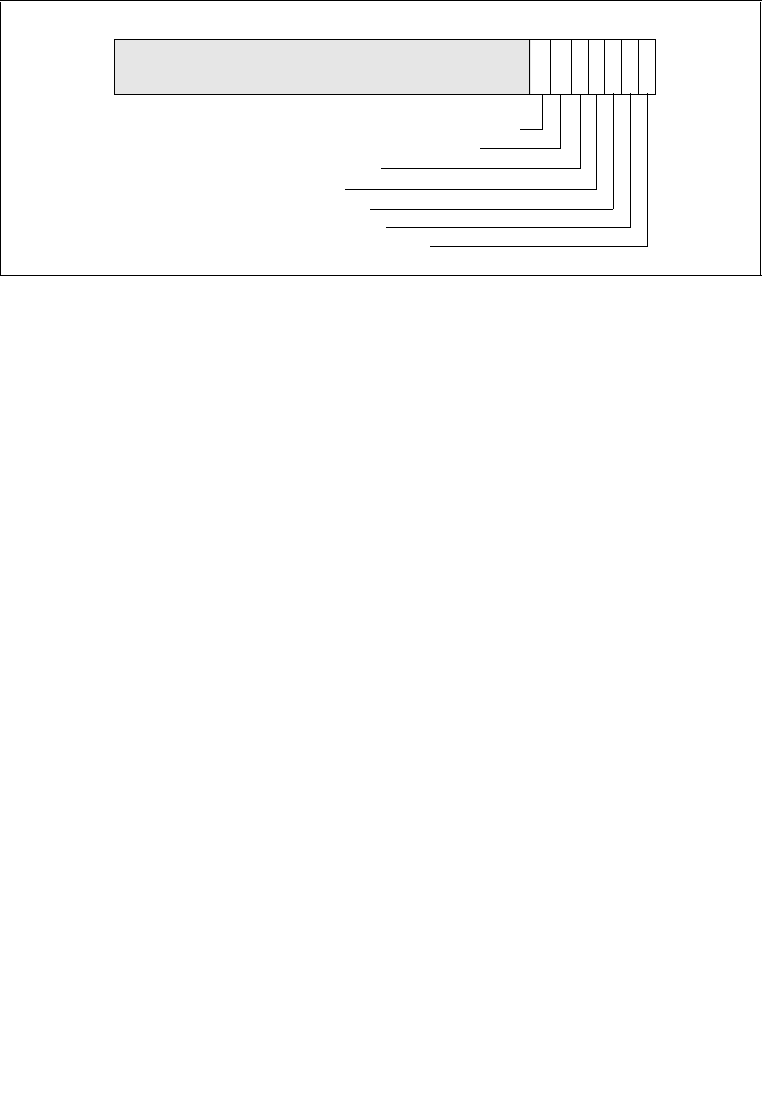

The initial implementation of BTS_OFF_USR and BTS_OFF_OS in

MSR_DEBUGCTLA is shown in Figure 16-12. The BTS_OFF_USR and

BTS_OFF_OS fields may be implemented on other model-specific

debug control register at different locations.

See Appendix B, “Model-Specific Registers (MSRs),” for a detailed description of each

of the last branch recording MSRs.

16.7.2 LBR Stack for Processors Based on Intel NetBurst

Microarchitecture

The LBR stack is made up of LBR MSRs that are treated by the processor as a circular

stack. The TOS pointer (MSR_LASTBRANCH_TOS MSR) points to the LBR MSR (or

Figure 16-12. MSR_DEBUGCTLA MSR for Pentium 4 and Intel Xeon Processors

31

TR — Trace messages enable

BTINT — Branch trace interrupt

BTF — Single-step on branches

LBR — Last branch/interrupt/exception

543

2

1

0

BTS — Branch trace store

Reserved

6

7

BTS_OFF_OS — Disable storing CPL_0 BTS

BTS_OFF_USR — Disable storing non-CPL_0 BTS