Vol. 3 6-29

INTERRUPT AND EXCEPTION HANDLING

Interrupt 1—Debug Exception (#DB)

Exception Class Trap or Fault. The exception handler can distinguish

between traps or faults by examining the contents of DR6

and the other debug registers.

Description

Indicates that one or more of several debug-exception conditions has been detected.

Whether the exception is a fault or a trap depends on the condition (see

Table 6-3).

See Chapter 16, “Debugging, Profiling Branches and Time-Stamp Counter,” for

detailed information about the debug exceptions.

Exception Error Code

None. An exception handler can examine the debug registers to determine which

condition caused the exception.

Saved Instruction Pointer

Fault — Saved contents of CS and EIP registers point to the instruction that gener-

ated the exception.

Trap — Saved contents of CS and EIP registers point to the instruction following the

instruction that generated the exception.

Program State Change

Fault — A program-state change does not accompany the debug exception, because

the exception occurs before the faulting instruction is executed. The program can

resume normal execution upon returning from the debug exception handler.

Trap — A program-state change does accompany the debug exception, because the

instruction or task switch being executed is allowed to complete before the exception

is generated. However, the new state of the program is not corrupted and execution

of the program can continue reliably.

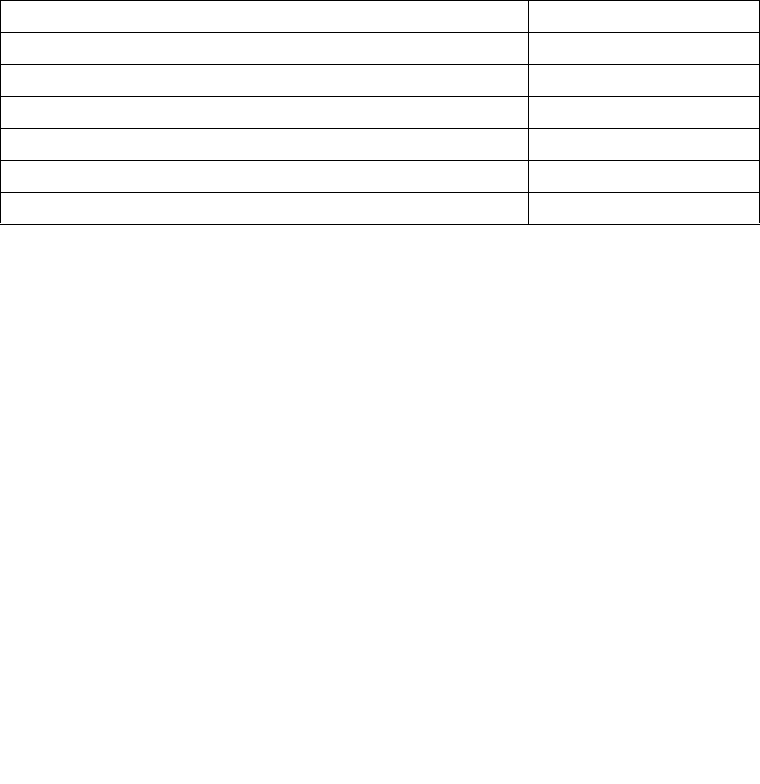

Table 6-3. Debug Exception Conditions and Corresponding Exception Classes

Exception Condition Exception Class

Instruction fetch breakpoint Fault

Data read or write breakpoint Trap

I/O read or write breakpoint Trap

General detect condition (in conjunction with in-circuit emulation) Fault

Single-step Trap

Task-switch Trap