Vol. 3 17-27

8086 EMULATION

Redirecting software interrupts back to the 8086 program potentially speeds up

interrupt handling because a switch back and forth between virtual-8086 mode and

protected mode is not required. This latter interrupt-handling technique is particu-

larly useful for 8086 operating systems (such as MS-DOS) that use the INT n instruc-

tion to call operating system procedures.

The CPUID instruction can be used to verify that the virtual mode extension is imple-

mented on the processor. Bit 1 of the feature flags register (EDX) indicates the avail-

ability of the virtual mode extension (see “CPUID—CPU Identification” in Chapter 3,

“Instruction Set Reference, A-M”, of the Intel® 64 and IA-32 Architectures Software

Developer’s Manual, Volume 2A).

The following sections describe the six methods (or mechanisms) for handling soft-

ware interrupts in virtual-8086 mode. See Section 17.3.2, “Class 2—Maskable Hard-

ware Interrupt Handling in Virtual-8086 Mode Using the Virtual Interrupt

Mechanism”, for a description of the use of the VIF and VIP flags in the EFLAGS

register for handling maskable hardware interrupts.

17.3.3.1 Method 1: Software Interrupt Handling

When the VME flag in control register CR4 is clear and the IOPL field is 3, a Pentium

or later IA-32 processor handles software interrupts in the same manner as they are

handled by an Intel386 or Intel486 processor. It executes an implicit call to the inter

-

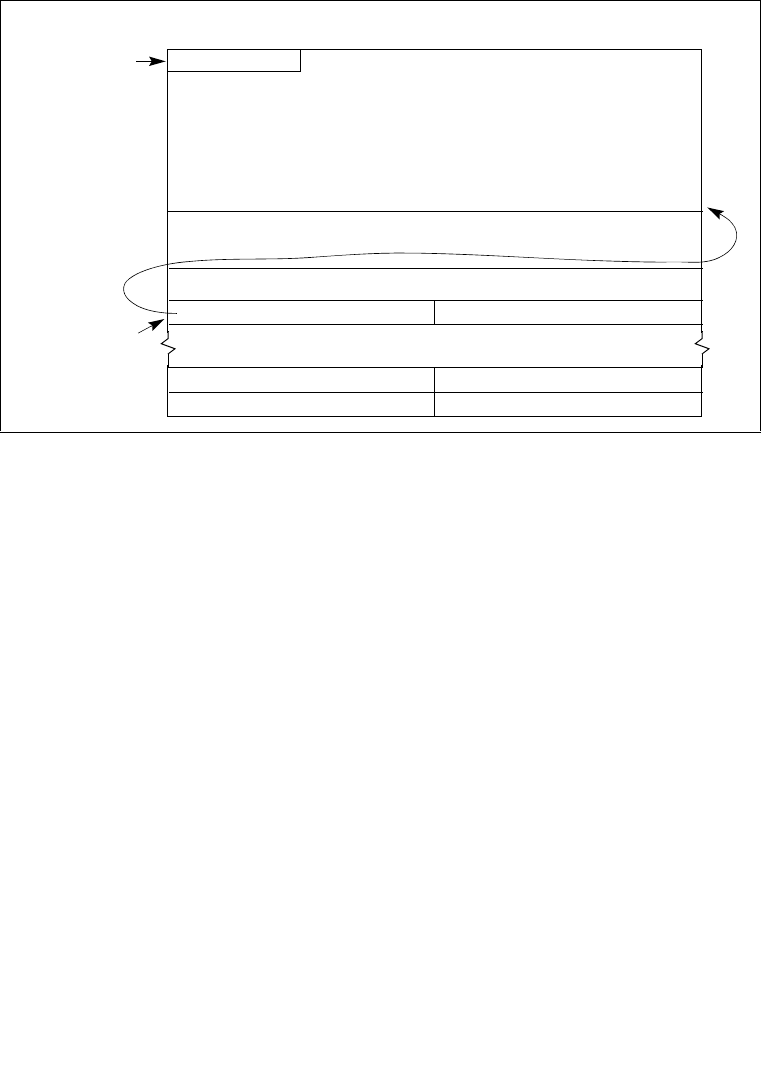

Figure 17-5. Software Interrupt Redirection Bit Map in TSS

I/O Map Base

Task-State Segment (TSS)

64H

31

24 23

0

1

1111111

I/O Permission Bit Map

0

I/O map

base must

not exceed

DFFFH.

Last byte of

bit

map must be

Software Interrupt Redirection Bit Map (32 Bytes)