Vol. 3 15-3

MACHINE-CHECK ARCHITECTURE

Each error-reporting bank is associated with a specific hardware unit (or

group of hardware units) in the processor. Use RDMSR and WRMSR to read

and to write these registers.

15.3.1 Machine-Check Global Control MSRs

The machine-check global control MSRs include the IA32_MCG_CAP,

IA32_MCG_STATUS, and IA32_MCG_CTL. See

Appendix B, “Model-Specific

Registers (MSRs),” for the addresses of these registers.

15.3.1.1 IA32_MCG_CAP MSR

The IA32_MCG_CAP MSR is a read-only register that provides information

about the machine-check architecture of the processor.

Figure 15-2 shows

the structure of the register in Pentium 4, Intel Xeon, and P6 family proces-

sors.

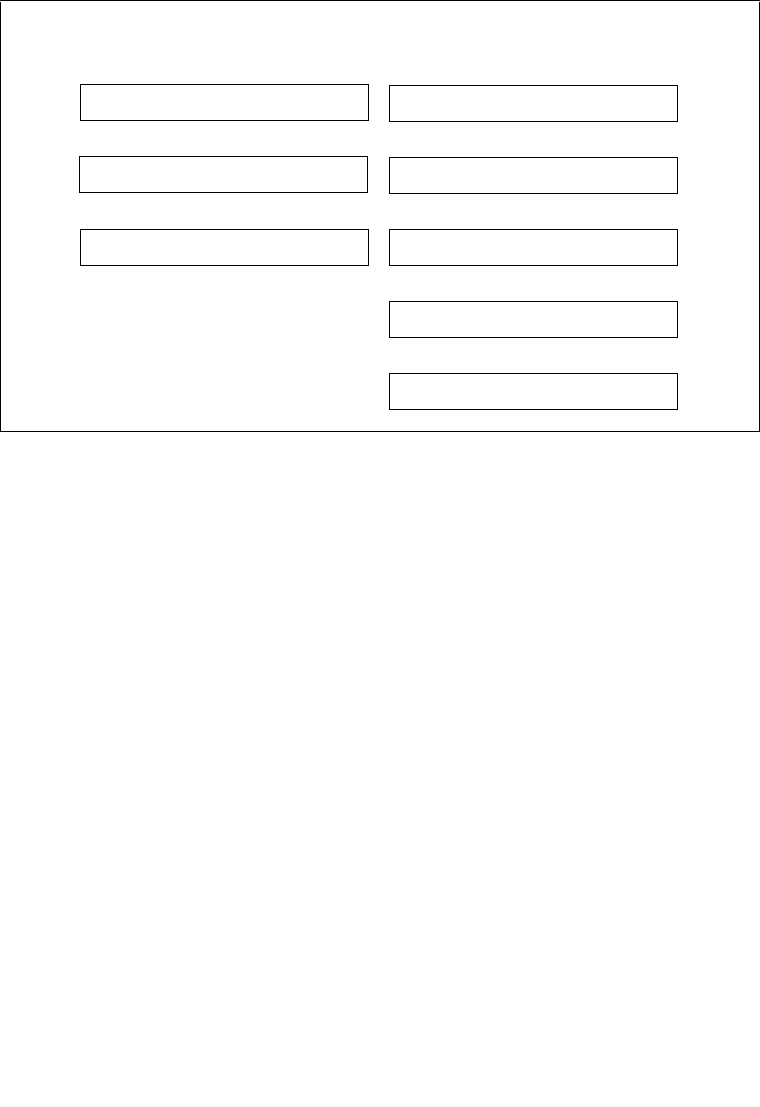

Figure 15-1. Machine-Check MSRs

0

63

0

63

IA32_MCG_CAP MSR

IA32_MCG_STATUS MSR

Error-Reporting Bank Registers

0

63

0

63

IA32_MCi_CTL MSR

IA32_MCi_STATUS MSR

0

63

0

63

IA32_MCi_ADDR MSR

IA32_MCi_MISC MSR

Global Control MSRs

(One Set for Each Hardware Unit)

0

63

IA32_MCG_CTL MSR

0

63

IA32_MCi_CTL2 MSR