9-4 Vol. 3

PROCESSOR MANAGEMENT AND INITIALIZATION

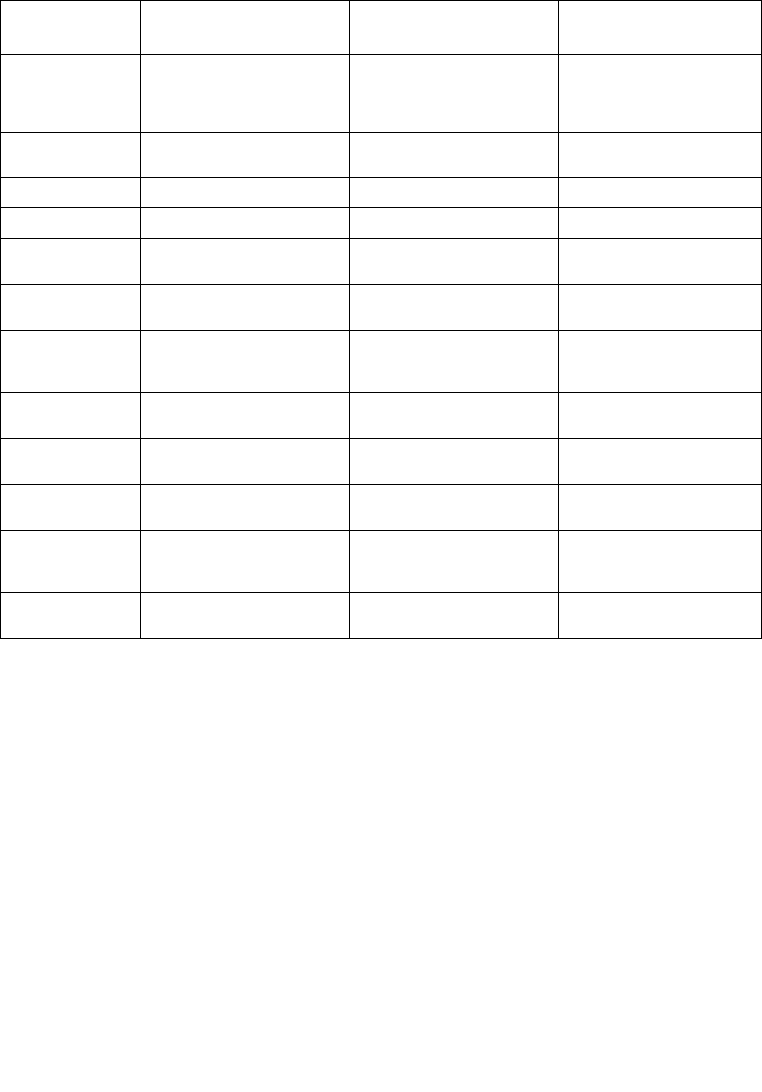

LDTR, Task

Register

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

DR0, DR1, DR2,

DR3

00000000H 00000000H 00000000H

DR6 FFFF0FF0H FFFF0FF0H FFFF0FF0H

DR7 00000400H 00000400H 00000400H

Time-Stamp

Counter

Power up or Reset: 0H

INIT: Unchanged

Power up or Reset: 0H

INIT: Unchanged

Power up or Reset: 0H

INIT: Unchanged

Perf. Counters and

Event Select

Power up or Reset: 0H

INIT: Unchanged

Power up or Reset: 0H

INIT: Unchanged

Power up or Reset: 0H

INIT: Unchanged

All Other MSRs Pwr up or Reset:

Undefined

INIT: Unchanged

Pwr up or Reset:

Undefined

INIT: Unchanged

Pwr up or Reset:

Undefined

INIT: Unchanged

Data and Code

Cache, TLBs

Invalid Invalid Invalid

Fixed MTRRs Pwr up or Reset: Disabled

INIT: Unchanged

Pwr up or Reset: Disabled

INIT: Unchanged

Not Implemented

Variable MTRRs Pwr up or Reset: Disabled

INIT: Unchanged

Pwr up or Reset: Disabled

INIT: Unchanged

Not Implemented

Machine-Check

Architecture

Pwr up or Reset:

Undefined

INIT: Unchanged

Pwr up or Reset:

Undefined

INIT: Unchanged

Not Implemented

APIC Pwr up or Reset: Enabled

INIT: Unchanged

Pwr up or Reset: Enabled

INIT: Unchanged

Pwr up or Reset: Enabled

INIT: Unchanged

NOTES:

1. The 10 most-significant bits of the EFLAGS register are undefined following a reset. Software

should not depend on the states of any of these bits.

2. The CD and NW flags are unchanged, bit 4 is set to 1, all other bits are cleared.

3. Where “n” is the Extended Model Value for the respective processor.

4. If Built-In Self-Test (BIST) is invoked on power up or reset, EAX is 0 only if all tests passed. (BIST

cannot be invoked during an INIT.)

5. The state of the x87 FPU and MMX registers is not changed by the execution of an INIT.

Table 9-1. IA-32 Processor States Following Power-up, Reset, or INIT (Contd.)

Register Pentium 4 and Intel

Xeon Processor

P6 Family Processor Pentium Processor