10-16 Vol. 3

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

10.5 EXTENDED XAPIC (X2APIC)

The x2APIC architecture extends the xAPIC architecture (described in Section 9.4) in

a backward compatible manner and provides forward extendability for future Intel

platform innovations. Specifically, x2APIC

• Retains all key elements of compatibility to the xAPIC architecture:

— delivery modes,

— interrupt and processor priorities,

— interrupt sources,

— interrupt destination types;

• Provides extensions to scale processor addressability for both the logical and

physical destination modes;

• Adds new features to enhance performance of interrupt delivery;

• Reduces complexity of logical destination mode interrupt delivery on link based

platform architectures.

• Uses MSR programming interface to access APIC registers in x2APIC mode

instead of memory-mapped interfaces. Memory-mapped interface is supported

when operating in xAPIC mode.

10.5.1 DETECTING AND ENABLING x2APIC

Processor support for x2APIC mode can be detected by executing CPUID with EAX=1

and then checking ECX, bit 21 ECX. If CPUID.(EAX=1):ECX.21 is set , the processor

supports the x2APIC capability and can be placed into the x2APIC mode.

• System software can place the local APIC in the x2APIC mode by setting the

x2APIC mode enable bit (bit 10) in the IA32_APIC_BASE MSR at MSR address

01BH. The layout for the IA32_APIC_BASE MSR is shown in

Figure 10-8.

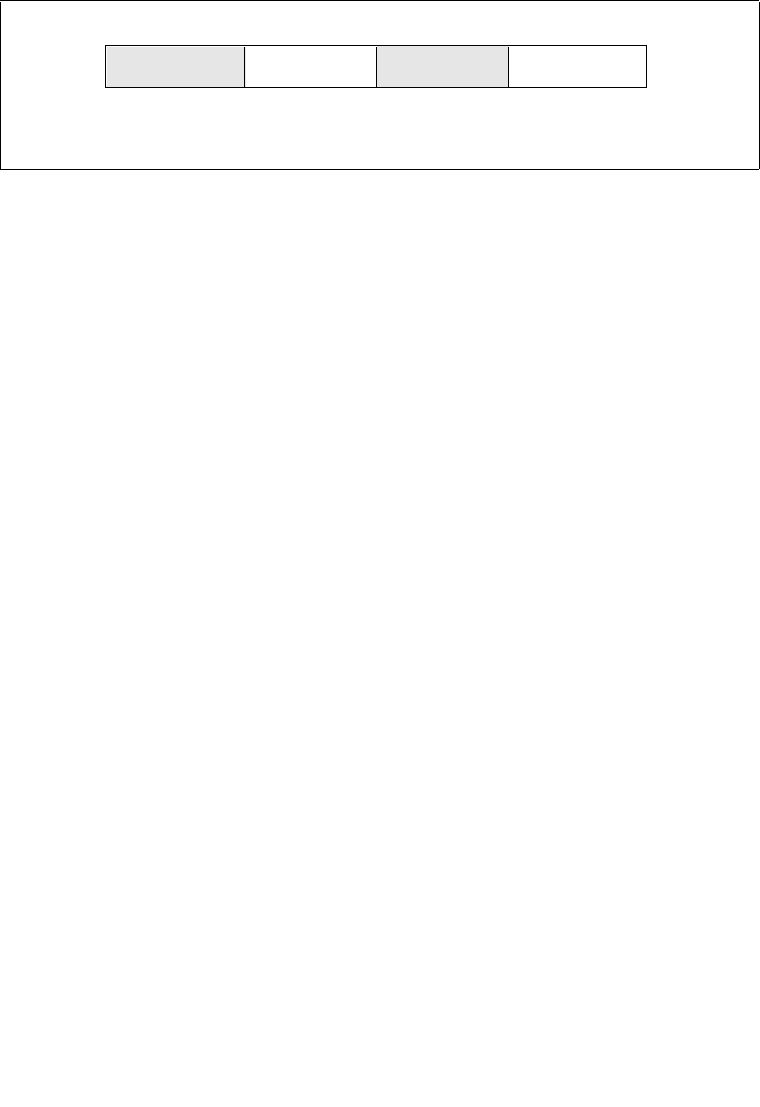

Figure 10-7. Local APIC Version Register

31

0

Reserved

2324 15

Version

Max. LVT

Value after reset: 000N 00VVH

V = Version, N = # of LVT entries minus 1

Entry

7

Address: FEE0 0030H

16 8

Reserved