15-34 Vol. 3

MACHINE-CHECK ARCHITECTURE

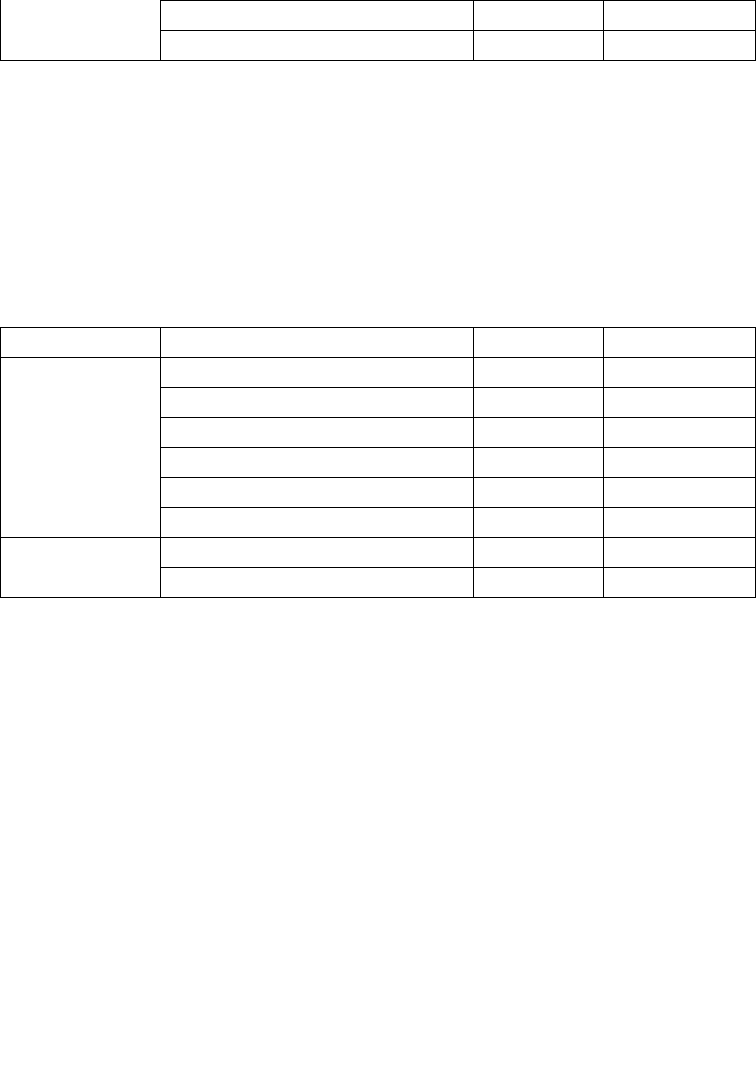

15.9.2.6 Memory Controller Errors

The memory controller errors are defined with the 3-bit MMM (memory

transaction type), and 4-bit CCCC (channel) sub-fields. The encodings for

MMM and CCCC are defined in

Table 15-14.

15.9.3 Architecturally Defined UCR Errors

Software recoverable compound error code are defined in this section.

15.9.3.1 Architecturally Defined SRAO Errors

The following two SRAO errors are architecturally defined.

• UCR Errors detected by memory controller scrubbing; and

• UCR Errors detected during L3 cache (L3) explicit writebacks.

The MCA error code encodings for these two architecturally-defined UCR

errors corresponds to sub-classes of compound MCA error codes (see

Table

I/O IO 10

Other transaction 11

NOTE:

* Local processor differentiates the processor reporting the error from other system components

(including the APIC, other processors, etc.).

Table 15-14. Encodings of MMM and CCCC Sub-Fields

Sub-Field Transaction Mnemonic Binary Encoding

MMM Generic undefined request GEN 000

Memory read error RD 001

Memory write error WR 010

Address/Command Error AC 011

Memory Scrubbing Error MS 100

Reserved 101-111

CCCC Channel number CHN 0000-1110

Channel not specified 1111

Table 15-13. Encodings of PP, T, and II Sub-Fields (Contd.)