10-34 Vol. 3

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

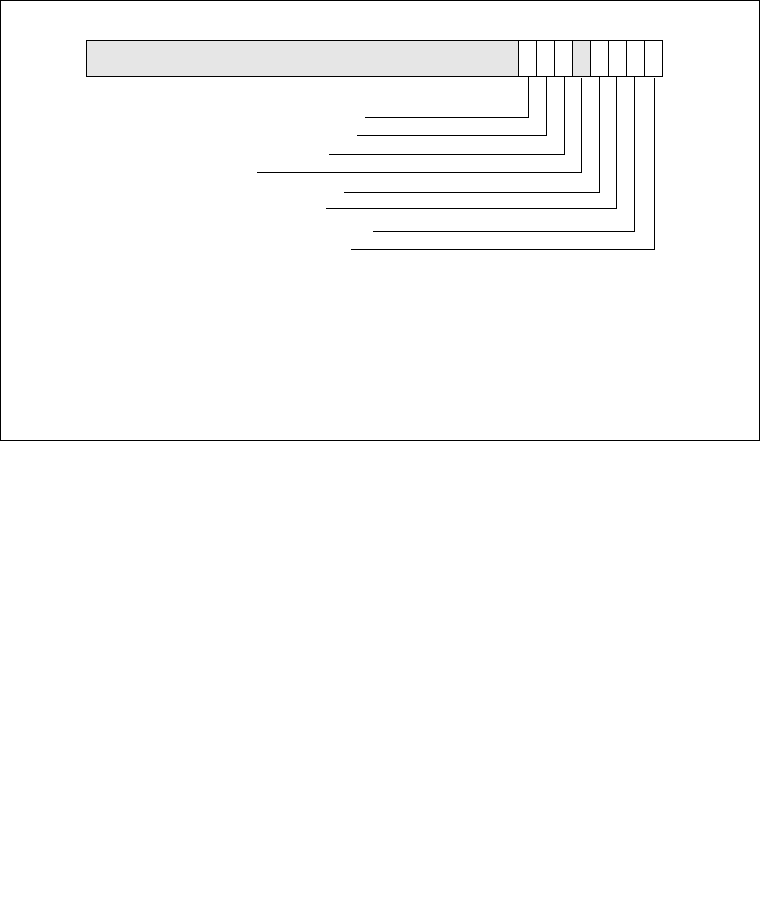

10.6.3 Error Handling

The local APIC provides an error status register (ESR) that it uses to record errors

that it detects when handling interrupts (see

Figure 10-13). An APIC error interrupt

is generated when the local APIC sets one of the error bits in the ESR. The LVT error

register allows selection of the interrupt vector to be delivered to the processor core

when APIC error is detected. The LVT error register also provides a means of masking

an APIC error interrupt.

The ESR is a write/read register. A write (of any value) to the ESR must be done just

prior to reading the ESR to update the register. This initial write causes the ESR

contents to be updated with the latest error status. Back-to-back writes clear the ESR

register. After an error bit is set in the register, it remains set until the register is

cleared.

The functions of the ESR are listed in Table 10-5.

Figure 10-13. Error Status Register (ESR)

Address: FEE0 0280H

Value after reset: 0H

31

0

Reserved

78123456

Illegal Register Address

1

Received Illegal Vector

Send Illegal Vector

Reserved

Receive Accept Error

2

Send Accept Error

2

Receive Checksum Error

2

Send Checksum Error

2

2. Only used in the P6 family and Pentium processors;

reserved in Intel Core, Pentium 4 and Intel Xeon processors.

1. Used in Intel Core, Pentium 4, Intel Xeon, and P6 family

processors; reserved in the Pentium processor.

NOTES: