Vol. 3 6-23

INTERRUPT AND EXCEPTION HANDLING

• The stack pointer (SS:RSP) is pushed unconditionally on interrupts. In legacy

modes, this push is conditional and based on a change in current privilege level

(CPL).

• The new SS is set to NULL if there is a change in CPL.

• IRET behavior changes.

• There is a new interrupt stack-switch mechanism.

• The alignment of interrupt stack frame is different.

6.14.1 64-Bit Mode IDT

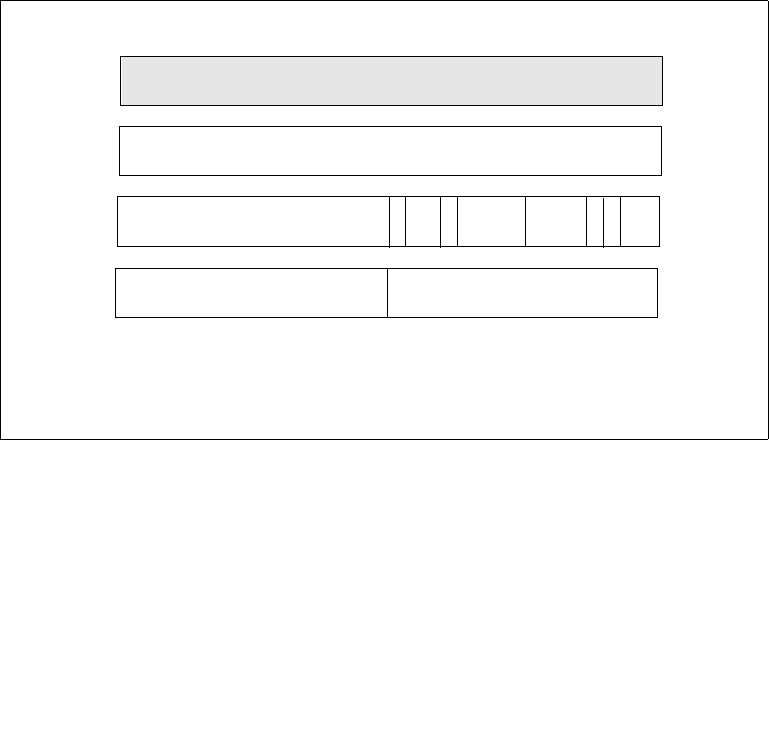

Interrupt and trap gates are 16 bytes in length to provide a 64-bit offset for the

instruction pointer (RIP). The 64-bit RIP referenced by interrupt-gate descriptors

allows an interrupt service routine to be located anywhere in the linear-address

space. See

Figure 6-7.

In 64-bit mode, the IDT index is formed by scaling the interrupt vector by 16. The

first eight bytes (bytes 7:0) of a 64-bit mode interrupt gate are similar but not iden

-

tical to legacy 32-bit interrupt gates. The type field (bits 11:8 in bytes 7:4) is

described in

Table 3-2. The Interrupt Stack Table (IST) field (bits 4:0 in bytes 7:4) is

used by the stack switching mechanisms described in Section 6.14.5, “Interrupt

Stack Table.” Bytes 11:8 hold the upper 32 bits of the target RIP (interrupt segment

offset) in canonical form. A general-protection exception (#GP) is generated if soft-

Figure 6-7. 64-Bit IDT Gate Descriptors

31

16

15

13

14 12

8

70

P

Offset 31..16

D

P

L

0

4

31

16

15

0

Segment Selector

Offset 15..0

0

TYPE

Interrupt/Trap Gate

DPL

Offset

P

Selector

Descriptor Privilege Level

Offset to procedure entry point

Segment Present flag

Segment Selector for destination code segment

45

0 0 0

31

0

Offset 63..32

8

31

0

12

11

IST

00

2

Reserved

IST

Interrupt Stack Table