19-6 Vol. 3

ARCHITECTURE COMPATIBILITY

19.13.1 Instructions Added Prior to the Pentium Processor

The following instructions were added in the Intel486 processor:

• BSWAP (byte swap) instruction.

• XADD (exchange and add) instruction.

• CMPXCHG (compare and exchange) instruction.

• ΙNVD (invalidate cache) instruction.

• WBINVD (write-back and invalidate cache) instruction.

• INVLPG (invalidate TLB entry) instruction.

The following instructions were added in the Intel386 processor:

• LSS, LFS, and LGS (load SS, FS, and GS registers).

• Long-displacement conditional jumps.

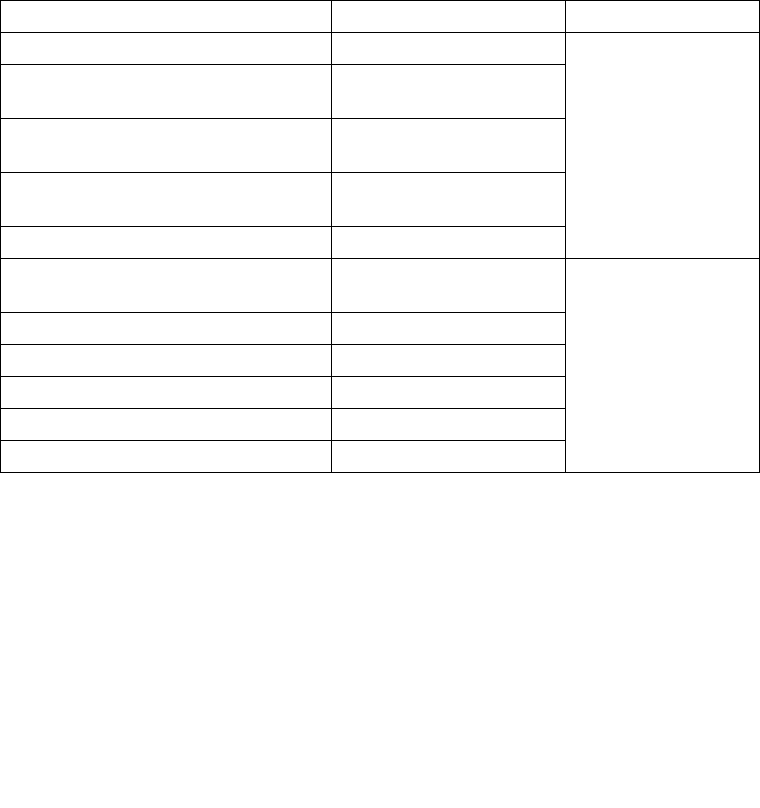

Table 19-1. New Instruction in the Pentium Processor and

Later IA-32 Processors

Instruction CPUID Identification Bits Introduced In

CMOVcc (conditional move) EDX, Bit 15 Pentium Pro processor

FCMOVcc (floating-point conditional

move)

EDX, Bits 0 and 15

FCOMI (floating-point compare and set

EFLAGS)

EDX, Bits 0 and 15

RDPMC (read performance monitoring

counters)

EAX, Bits 8-11, set to 6H;

see Note 1

UD2 (undefined) EAX, Bits 8-11, set to 6H

CMPXCHG8B (compare and exchange 8

bytes)

EDX, Bit 8 Pentium processor

CPUID (CPU identification) None; see Note 2

RDTSC (read time-stamp counter) EDX, Bit 4

RDMSR (read model-specific register) EDX, Bit 5

WRMSR (write model-specific register) EDX, Bit 5

MMX Instructions EDX, Bit 23

NOTES:

1. The RDPMC instruction was introduced in the P6 family of processors and added to later model

Pentium processors. This instruction is model specific in nature and not architectural.

2. The CPUID instruction is available in all Pentium and P6 family processors and in later models of

the Intel486 processors. The ability to set and clear the ID flag (bit 21) in the EFLAGS register

indicates the availability of the CPUID instruction.