Vol. 3 4-11

PAGING

Because a PDE is identified using bits 31:22 of the linear address, it controls access

to a 4-Mbyte region of the linear-address space. Use of the PDE depends on CR.PSE

and the PDE’s PS flag (bit 7):

• If CR4.PSE = 1 and the PDE’s PS flag is 1, the PDE maps a 4-MByte page (see

Table 4-4). The final physical address is computed as follows:

— Bits 39:32 are bits 20:13 of the PDE.

— Bits 31:22 are bits 31:22 of the PDE.

1

— Bits 21:0 are from the original linear address.

• If CR4.PSE = 0 or the PDE’s PS flag is 0, a 4-KByte naturally aligned page table is

located at the physical address specified in bits 31:12 of the PDE (see Table 4-5).

A page table comprises 1024 32-bit entries (PTEs). A PTE is selected using the

physical address defined as follows:

— Bits 39:32 are all 0.

— Bits 31:12 are from the PDE.

— Bits 11:2 are bits 21:12 of the linear address.

— Bits 1:0 are 0.

• Because a PTE is identified using bits 31:12 of the linear address, every PTE

maps a 4-KByte page (see Table 4-6). The final physical address is computed as

follows:

— Bits 39:32 are all 0.

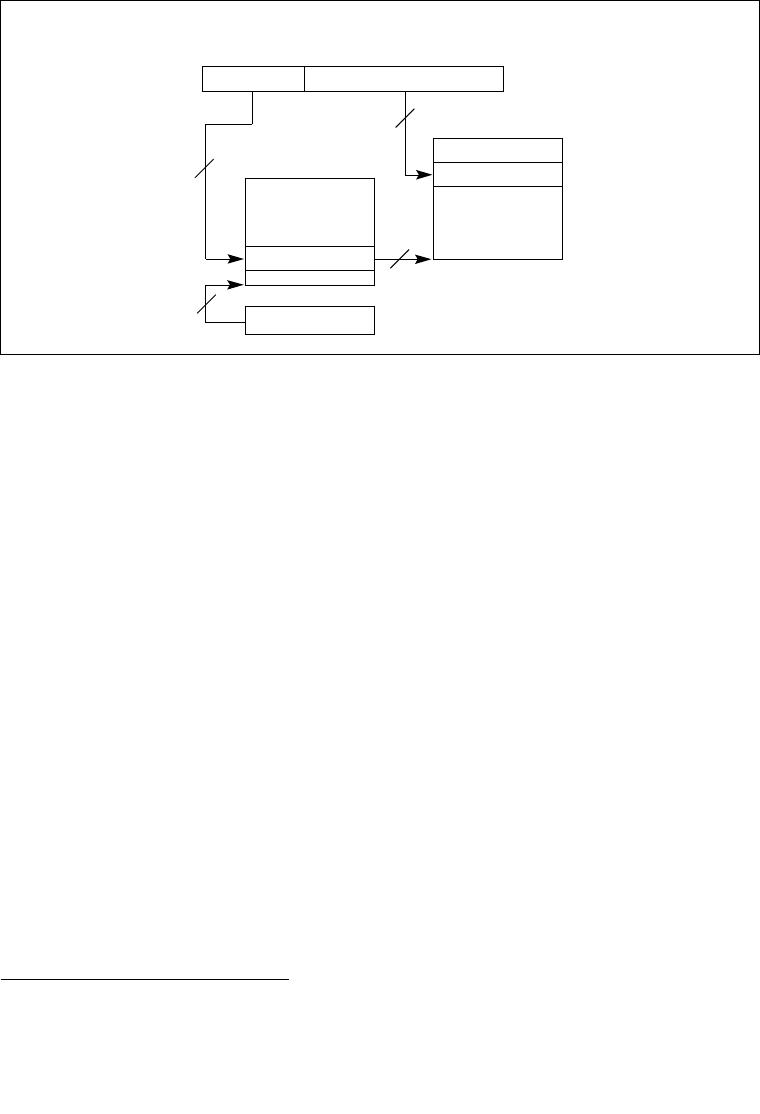

Figure 4-3. Linear-Address Translation to a 4-MByte Page using 32-Bit Paging

1. The upper bits in the final physical address do not all come from corresponding positions in the

PDE; the physical-address bits in the PDE are not all contiguous.

0

Directory

Offset

Page Directory

PDE with PS=1

CR3

4-MByte Page

Physical Address

31 2122

Linear Address

10

22

32

18