16-44 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

— TR (trace message enable) flag (bit 6) — When set, branch trace

messages are enabled. When the processor detects a taken branch,

interrupt, or exception, it sends the branch record out on the system bus as a

branch trace message (BTM). See Section 16.4.4, “Branch Trace Messages,”

for more information about the TR flag.

— BTS (branch trace store) flag (bit 7) — When set, enables the BTS

facilities to log BTMs to a memory-resident BTS buffer that is part of the DS

save area. See Section 16.4.9, “BTS and DS Save Area.”

— BTINT (branch trace interrupt) flag (bits 8) — When set, the BTS

facilities generate an interrupt when the BTS buffer is full. When clear, BTMs are

logged to the BTS buffer in a circular fashion. See Section 16.4.5, “Branch Trace

Store (BTS),” for a description of this mechanism.

• Debug store (DS) feature flag (bit 21), returned by the CPUID

instruction — Indicates that the processor provides the debug store (DS)

mechanism, which allows BTMs to be stored in a memory-resident BTS buffer.

See Section 16.4.5, “Branch Trace Store (BTS).”

• Last Branch Record (LBR) Stack — The LBR stack consists of 8 MSRs

(MSR_LASTBRANCH_0 through MSR_LASTBRANCH_7); bits 31-0 hold the ‘from’

address, bits 63-32 hold the ‘to’ address. For Pentium M Processors, these pairs

are located at register addresses 040H-047H. See Figure 16-17.

• Last Branch Record Top-of-Stack (TOS) Pointer — The TOS Pointer MSR

contains a 3-bit pointer (bits 2-0) to the MSR in the LBR stack that contains the

most recent branch, interrupt, or exception recorded. For Pentium M Processors,

this MSR is located at register address 01C9H.

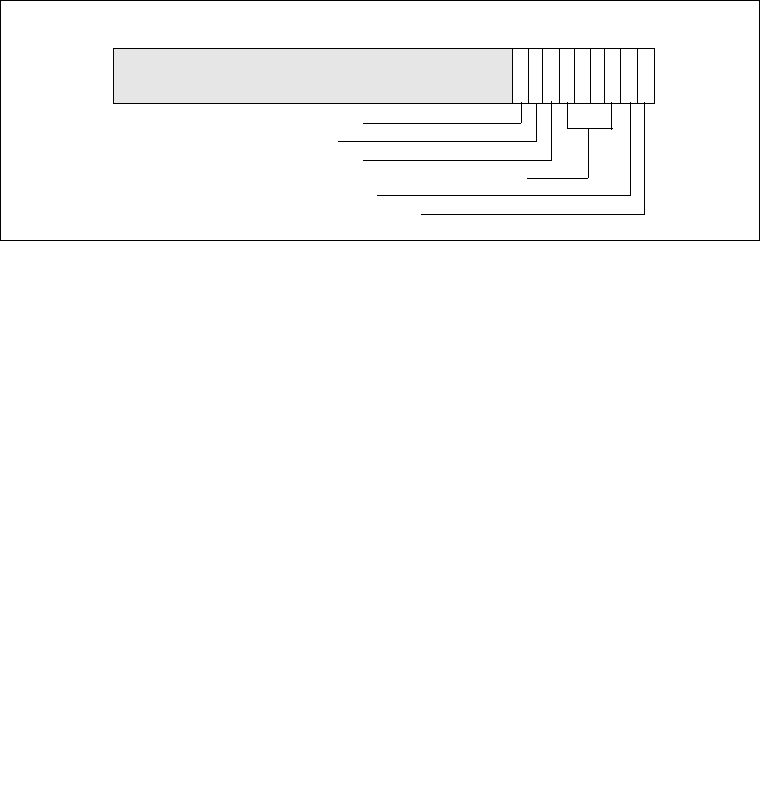

Figure 16-16. MSR_DEBUGCTLB MSR for Pentium M Processors

31

TR — Trace messages enable

BTINT — Branch trace interrupt

BTF — Single-step on branches

LBR — Last branch/interrupt/exception

Reserved

87654321 0

BTS — Branch trace store

PB3/2/1/0 — Performance monitoring breakpoint flags