Vol. 3 8-49

MULTIPLE-PROCESSOR MANAGEMENT

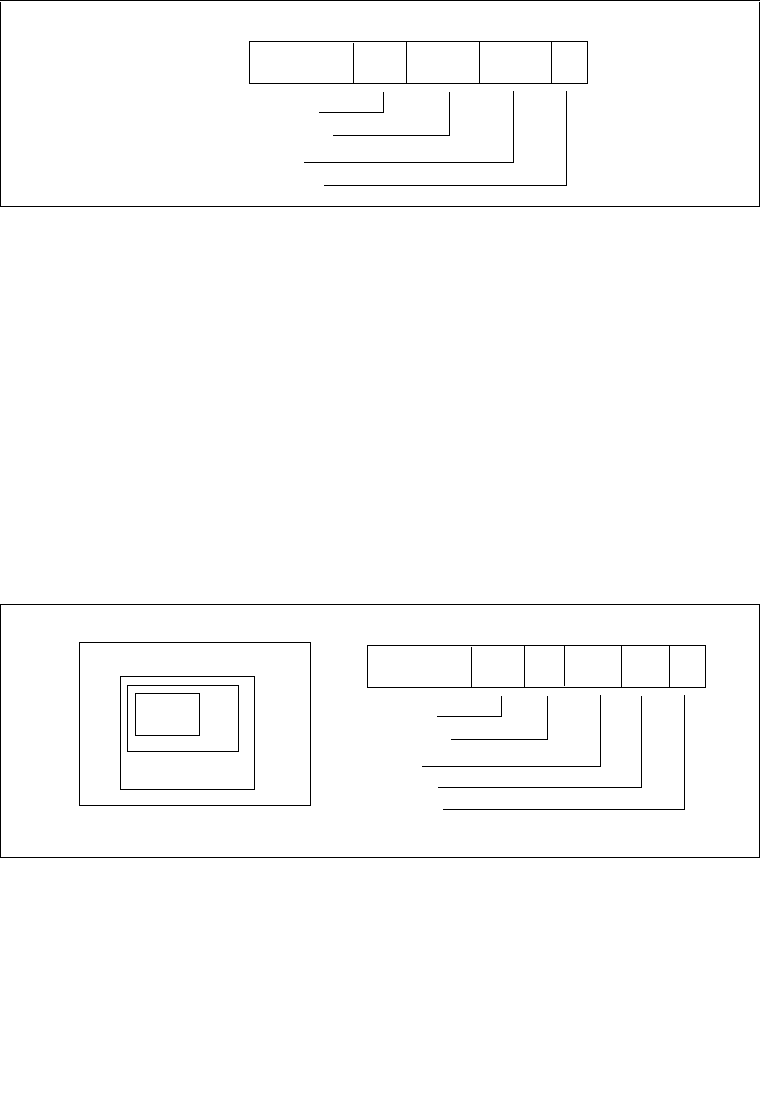

If the processor supports CPUID leaf 0BH, the 32-bit APIC ID can represent cluster

plus several levels of topology within the physical processor package. The exact

number of hierarchical levels within a physical processor package must be enumer

-

ated through CPUID leaf 0BH. Common processor families may employ topology

similar to that represented by 8-bit Initial APIC ID. In general, CPUID leaf 0BH can

support topology enumeration algorithm that decompose a 32-bit APIC ID into more

than four sub-fields (see

Figure 8-6).

The width of each sub-field depends on hardware and software configurations. Field

widths can be determined at runtime using the algorithm discussed below (Example

8-16 through Example 8-20).

Figure 7-6 depicts the relationships of three of the hierarchical sub-fields in a hypo-

thetical MP system. The value of valid APIC_IDs need not be contiguous across

package boundary or core boundaries.

Figure 8-5. Generalized Four level Interpretation of the APIC ID

Figure 8-6. Conceptual Five-level Topology and 32-bit APIC ID Composition

0

Package ID

SMT ID

X

Cluster ID

Reserved

Core ID

X=31 if x2APIC is supported

Otherwise X= 7

0

Package ID

R ID

31

Cluster ID

Reserved

Q ID

SMT ID

R

SMT

Q

Package

Physical Processor Topology

32-bit APIC ID Composition