Vol. 3 10-7

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

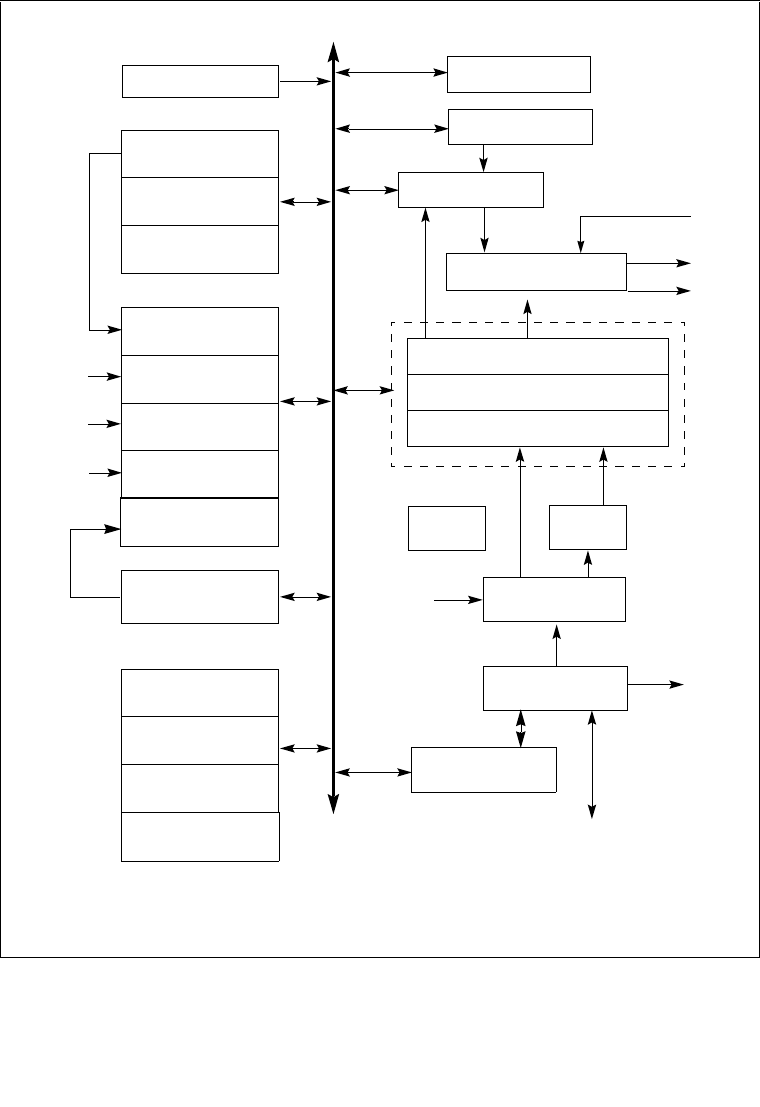

Figure 10-4. Local APIC Structure

Current Count

Register

Initial Count

Register

Divide Configuration

Register

Version Register

Error Status

Register

In-Service Register (ISR)

Vector

Decode

Interrupt Command

Register (ICR)

Acceptance

Logic

Vec[3:0]

& TMR Bit

Register

Select

INIT

NMI

SMI

Protocol

Translation Logic

Dest. Mode

& Vector

Processor System Bus

3

APIC ID

Register

Logical Destination

Register

Destination Format

Register

Timer

Local

Interrupts 0,1

Performance

Monitoring Counters

1

Error

Timer

Local Vector Table

DATA/ADDR

Prioritizer

Task Priority Register

EOI Register

INTR

EXTINT

INTA

LINT0/1

1. Introduced in P6 family processors.

Thermal Sensor

2

2. Introduced in the Pentium 4 and Intel Xeon processors.

Perf. Mon.

Thermal

(Internal

Interrupt)

Sensor

(Internal

Interrupt)

Spurious Vector

Register

Local

Interrupts

3. Three-wire APIC bus in P6 family and Pentium processors.

To

CPU

Core

From

CPU

Core

Interrupt Request Register (IRR)

Trigger Mode Register (TMR)

To

CPU

Core

Processor Priority

Register

4. Not implemented in Pentium 4 and Intel Xeon processors.

Arb. ID

Register

4