16-30 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

2. Set the TR and BTS flags in the IA32_DEBUGCTL for Intel Core Solo and Intel

Core Duo processors or later processors (or MSR_DEBUGCTLA MSR for

processors based on Intel NetBurst Microarchitecture; or MSR_DEBUGCTLB for

Pentium M processors).

3. Clear the BTINT flag in the corresponding IA32_DEBUGCTL (or MSR_DEBUGCTLA

MSR; or MSR_DEBUGCTLB) if a circular BTS buffer is desired.

NOTES

If the buffer size is set to less than the minimum allowable value (i.e.

BTS absolute maximum < 1 + size of BTS record), the results of BTS

is undefined.

In order to prevent generating an interrupt, when working with

circular BTS buffer, SW need to set BTS interrupt threshold to a value

greater than BTS absolute maximum (fields of the DS buffer

management area). It's not enough to clear the BTINT flag itself only.

16.4.9.4 Setting Up CPL-Qualified BTS

If the processor supports CPL-qualified last branch recording mechanism, the gener-

ation of branch records and storing of them in the BTS buffer are determined by: TR,

BTS, BTS_OFF_OS, BTS_OFF_USR, and BTINT. The encoding of these five bits are

shown in Table 16-5.

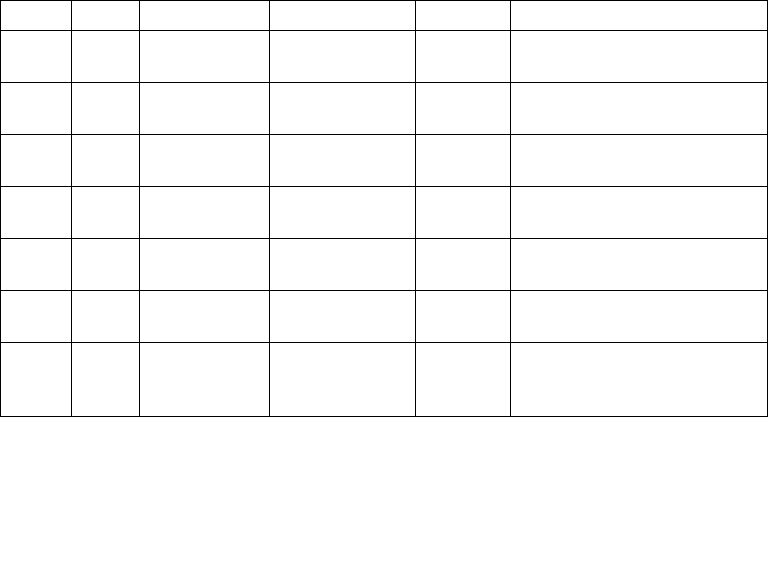

Table 16-5. CPL-Qualified Branch Trace Store Encodings

TR BTS BTS_OFF_OS BTS_OFF_USR BTINT Description

0 X X X X Branch trace messages (BTMs)

off

1 0 X X X Generates BTMs but do not

store BTMs

1 1 0 0 0 Store all BTMs in the BTS buffer,

used here as a circular buffer

1 1 1 0 0 Store BTMs with CPL > 0 in the

BTS buffer

1 1 0 1 0 Store BTMs with CPL = 0 in the

BTS buffer

1 1 1 1 X Generate BTMs but do not store

BTMs

1 1 0 0 1 Store all BTMs in the BTS buffer;

generate an interrupt when the

buffer is nearly full