11-30 Vol. 3

MEMORY CACHE CONTROL

The discussion of write ordering in Section 8.2, “Memory Ordering,” gives a detailed

description of the operation of the store buffer.

11.11 MEMORY TYPE RANGE REGISTERS (MTRRS)

The following section pertains only to the P6 and more recent processor families.

The memory type range registers (MTRRs) provide a mechanism for associating the

memory types (see

Section 11.3, “Methods of Caching Available”) with physical-

address ranges in system memory. They allow the processor to optimize operations

for different types of memory such as RAM, ROM, frame-buffer memory, and

memory-mapped I/O devices. They also simplify system hardware design by elimi

-

nating the memory control pins used for this function on earlier IA-32 processors and

the external logic needed to drive them.

The MTRR mechanism allows up to 96 memory ranges to be defined in physical

memory, and it defines a set of model-specific registers (MSRs) for specifying the

type of memory that is contained in each range.

Table 11-8 shows the memory types

that can be specified and their properties; Figure 11-4 shows the mapping of physical

memory with MTRRs. See Section 11.3, “Methods of Caching Available,” for a more

detailed description of each memory type.

Following a hardware reset, the P6 and more recent processor families disable all the

fixed and variable MTRRs, which in effect makes all of physical memory uncacheable.

Initialization software should then set the MTRRs to a specific, system-defined

memory map. Typically, the BIOS (basic input/output system) software configures

the MTRRs. The operating system or executive is then free to modify the memory

map using the normal page-level cacheability attributes.

In a multiprocessor system using a processor in the P6 family or a more recent

family, each processor MUST use the identical MTRR memory map so that software

will have a consistent view of memory.

NOTE

In multiple processor systems, the operating system must maintain

MTRR consistency between all the processors in the system (that is,

all processors must use the same MTRR values). The P6 and more

recent processor families provide no hardware support for

maintaining this consistency.

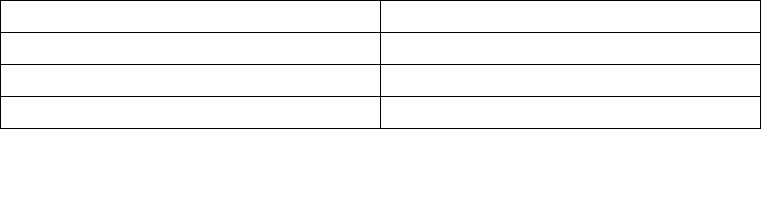

Table 11-8. Memory Types That Can Be Encoded in MTRRs

Memory Type and Mnemonic Encoding in MTRR

Uncacheable (UC) 00H

Write Combining (WC) 01H

Reserved* 02H