18-6 Vol. 3

MIXING 16-BIT AND 32-BIT CODE

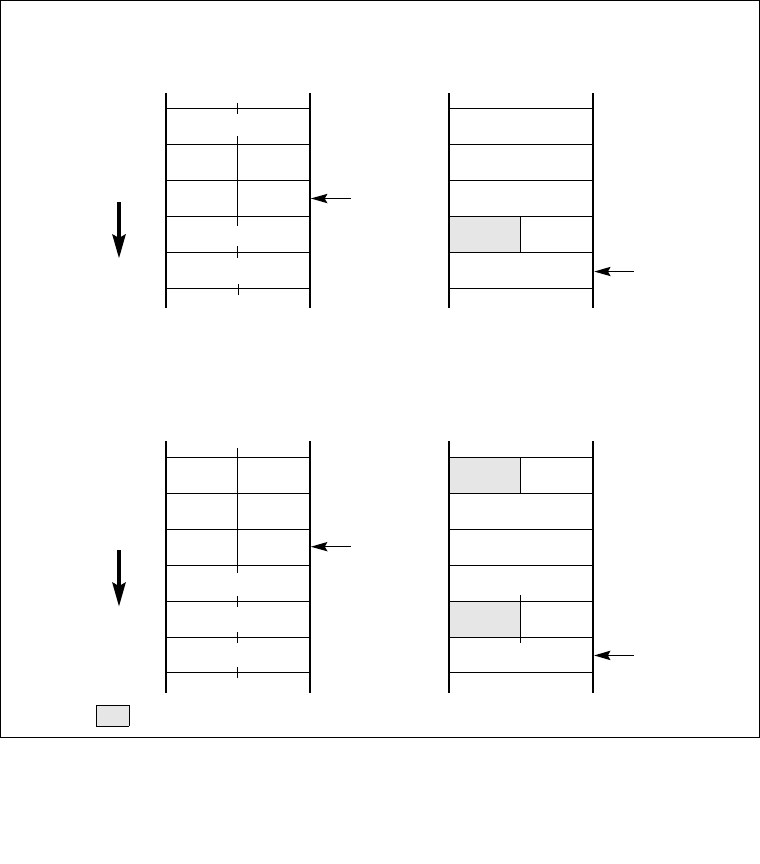

instruction (see Figure 18-1). On a 16-bit call, the processor pushes the contents of

the 16-bit IP register and (for calls between privilege levels) the 16-bit SP register.

The matching RET instruction must also use a 16-bit operand size to pop these 16-bit

values from the stack into the 16-bit registers.

A 32-bit CALL instruction pushes the contents of the 32-bit EIP register and (for

inter-privilege-level calls) the 32-bit ESP register. Here, the matching RET instruction

must use a 32-bit operand size to pop these 32-bit values from the stack into the

32-bit registers. If the two parts of a CALL/RET instruction pair do not have matching

operand sizes, the stack will not be managed correctly and the values of the instruc

-

tion pointer and stack pointer will not be restored to correct values.

Figure 18-1. Stack after Far 16- and 32-Bit Calls

SP

After 16-bit Call

PARM 1

IP

SP

SS

PARM 2

CS

031

SS

EIP

After 32-bit Call

CS

ESP

ESP

PARM 2

PARM 1

031

With Privilege Transition

Stack

Growth

After 16-bit Call

PARM 1

IP

SP

PARM 2

CS

031

Without Privilege Transition

Stack

Growth

After 32-bit Call

PARM 1

ESP

PARM 2

CS

031

EIP

Undefined