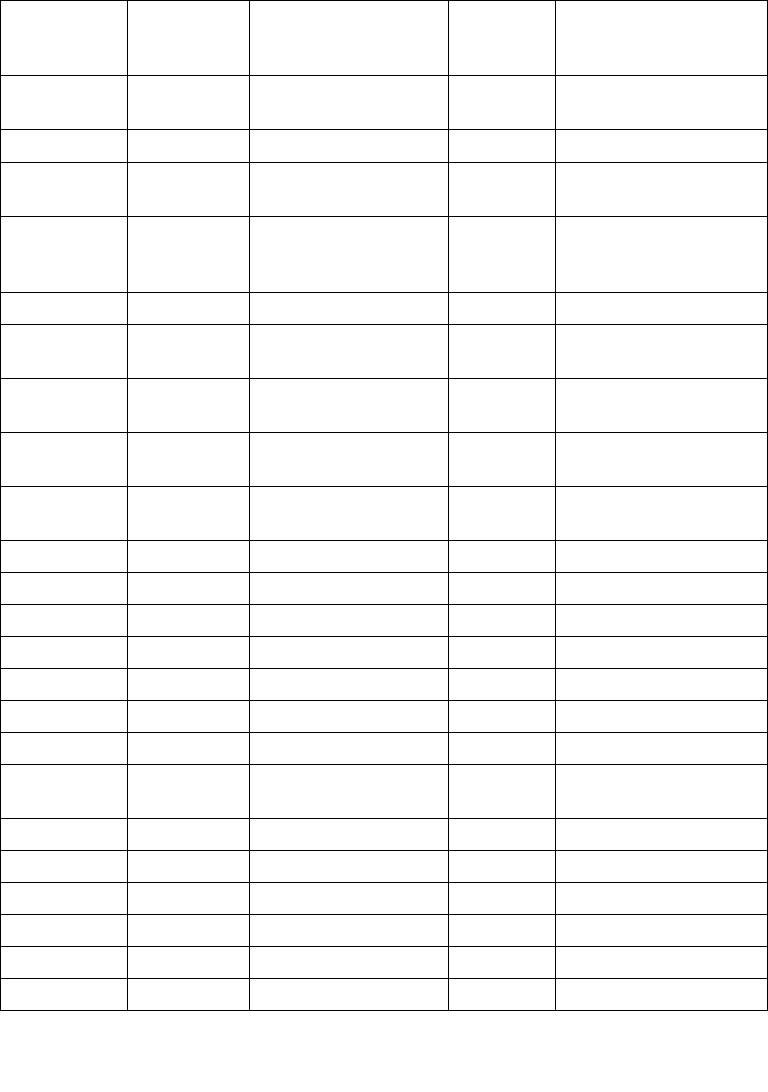

Vol. 3 10-19

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

0080H 008H Task Priority Register

(TPR)

Read/Write. Bits 7:0 are RW. Bits 31:8

are Reserved.

0090H 009H Reserved

00A0H 00AH Processor Priority

Register (PPR)

Read only.

00B0H 00BH EOI Register Write only. 0 is the only valid value

to write. GP fault on non-

zero write

00C0H 00CH Reserved

00D0H 00DH Logical Destination

Register

Read only. Read/Write in xAPIC

mode)

00E0H 00EH Reserved

1

GP fault on Read Write in

x2APIC mode.

00F0H 00FH Spurious Interrupt

Vector Register

Read/Write. Bits 0-8, 12 Read/Write;

other bits reserved.

0100H 010H In-Service Register

(ISR); bits 0:31

Read Only.

0110H 011H ISR bits 32:63 Read Only.

0120H 012H ISR bits 64:95 Read Only.

0130H 013H ISR bits 96:127 Read Only.

0140H 014H ISR bits 128:159 Read Only.

0150H 015H ISR bits 160:191 Read Only.

0160H 016H ISR bits 192:223 Read Only.

0170H 017H ISR bits 224:255 Read Only.

0180H 018H Trigger Mode Register

(TMR); bits 0:31

Read Only.

0190H 019H TMR bits 32:63 Read Only.

01A0H 01AH TMR bits 64:95 Read Only.

01B0H 01BH TMR bits 96:127 Read Only.

01C0H 01CH TMR bits 128:159 Read Only.

01D0H 01DH TMR bits 160:191 Read Only.

01E0H 01EH TMR bits 192:223 Read Only.

Table 10-3. Local APIC Register Address Map Supported by x2APIC (Contd.)

MMIO Offset

(xAPIC mode)

MSR Offset

(x2APIC

mode) Register Name

R/W

Semantics Comments