15-32 Vol. 3

MACHINE-CHECK ARCHITECTURE

The behavior of error filtering after crossing the yellow threshold is model-

specific.

15.9.2.2 Transaction Type (TT) Sub-Field

The 2-bit TT sub-field (Table 15-10) indicates the type of transaction (data,

instruction, or generic). The sub-field applies to the TLB, cache, and inter-

connect error conditions. Note that interconnect error conditions are prima-

rily associated with P6 family and Pentium processors, which utilize an

external APIC bus separate from the system bus. The generic type is

reported when the processor cannot determine the transaction type.

15.9.2.3 Level (LL) Sub-Field

The 2-bit LL sub-field (see Table 15-11) indicates the level in the memory

hierarchy where the error occurred (level 0, level 1, level 2, or generic). The

LL sub-field also applies to the TLB, cache, and interconnect error condi

-

tions. The Pentium 4, Intel Xeon, and P6 family processors support two

levels in the cache hierarchy and one level in the TLBs. Again, the generic

type is reported when the processor cannot determine the hierarchy level.

15.9.2.4 Request (RRRR) Sub-Field

The 4-bit RRRR sub-field (see Table 15-12) indicates the type of action asso-

ciated with the error. Actions include read and write operations, prefetches,

cache evictions, and snoops. Generic error is returned when the type of error

cannot be determined. Generic read and generic write are returned when

the processor cannot determine the type of instruction or data request that

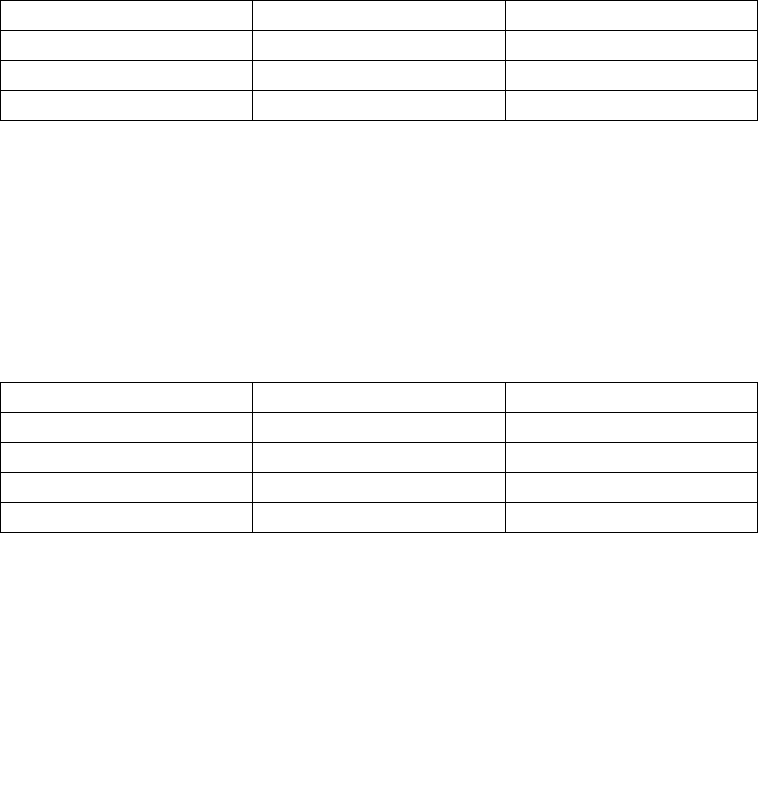

Table 15-10. Encoding for TT (Transaction Type) Sub-Field

Transaction Type Mnemonic Binary Encoding

Instruction I 00

Data D 01

Generic G 10

Table 15-11. Level Encoding for LL (Memory Hierarchy Level) Sub-Field

Hierarchy Level Mnemonic Binary Encoding

Level 0 L0 00

Level 1 L1 01

Level 2 L2 10

Generic LG 11