10-36 Vol. 3

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

If the ICR is programmed with lowest priority delivery mode then the "Re-directible

IPI" bit will be set in x2APIC modes (same as legacy xAPIC behavior) and the inter-

rupt will not be processed.

Write to the ICR with both lowest priority delivery mode and illegal vector, will set the

"re-directible IPI" error bit. The interrupt will not be processed and hence the "Send

Illegal Vector" error bit will not be set.

10.6.4 APIC Timer

The local APIC unit contains a 32-bit programmable timer that is available to soft-

ware to time events or operations. This timer is set up by programming four regis-

ters: the divide configuration register (see Figure 10-15), the initial-count and

current-count registers (see Figure 10-16), and the LVT timer register (see

Figure 10-12).

If CPUID.06H:EAX.ARAT[bit 2] = 1, the processor’s APIC timer runs at a constant

rate regardless of P-state transitions and it continues to run at the same rate in deep

C-states.

If CPUID.06H:EAX.ARAT[bit 2] = 0 or if CPUID 06H is not supported, the APIC timer

may temporarily stop while the processor is in deep C-states or during transitions

caused by Enhanced Intel SpeedStep® Technology.

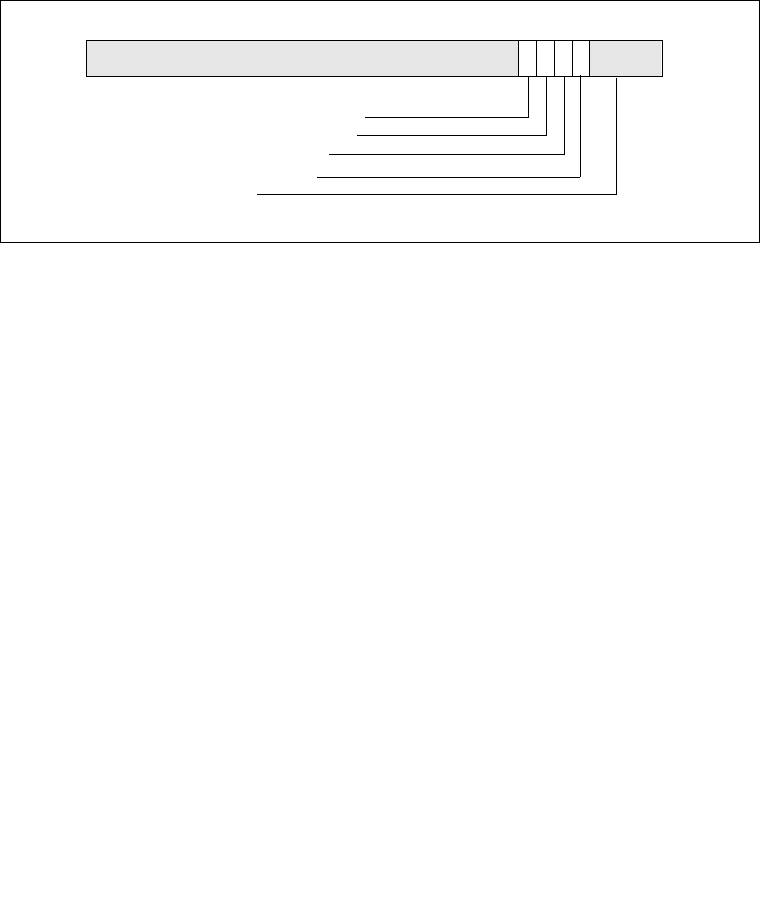

Figure 10-14. Error Status Register (ESR) in x2APIC Mode

MSR Address: 828H

31

0

Reserved

78123456

Illegal Register Address

Received Illegal Vector

Send Illegal Vector

Redirectible IPI

Reserved