10-4 Vol. 3

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

also be delivered to the individual processors through the local interrupt pins;

however, this mechanism is commonly not used in MP systems.

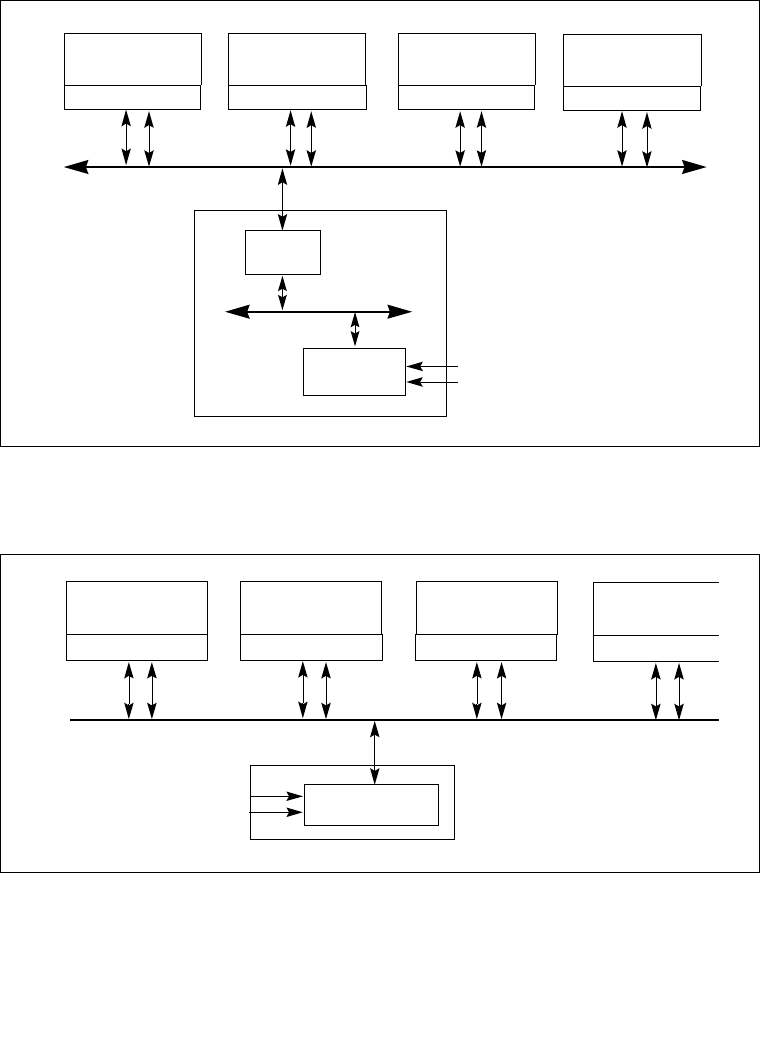

Figure 10-2. Local APICs and I/O APIC When Intel Xeon Processors Are Used in

Multiple-Processor

Systems

Figure 10-3. Local APICs and I/O APIC When P6 Family Processors Are Used in

Multiple-Processor Systems

I/O APIC

External

Interrupts

System Chip Set

Processor System Bus

CPU

Local APIC

Processor #2

CPU

Local APIC

Processor #3

CPU

Local APIC

Processor #1

CPU

Local APIC

Processor #3

Bridge

PCI

IPIs IPIs IPIs

Interrupt

Messages

IPIs

Interrupt

Messages

Interrupt

Messages

Interrupt

Messages

Interrupt

Messages

CPU

Local APIC

P

rocessor

#2

CPU

Local APIC

P

rocessor

#3

CPU

Local APIC

P

rocessor

#1

Interrupt

Messages

I/O APIC

External

Interrupts

System Chip Set

3-wire APIC Bus

CPU

Local APIC

P

rocessor

#4

IPIs

IPIs

IPIs

IPIs

Interrupt

Messages

Interrupt

Messages

Interrupt

Messages

Interrupt

Messages