16-46 Vol. 3

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

• BTF (single-step on branches) flag (bit 1) — When set, the processor treats

the TF flag in the EFLAGS register as a “single-step on branches” flag. See

Section 16.4.3, “Single-Stepping on Branches, Exceptions, and Interrupts.”

• PBi (performance monitoring/breakpoint pins) flags (bits 2 through 5)

— When these flags are set, the performance monitoring/breakpoint pins on the

processor (BP0#, BP1#, BP2#, and BP3#) report breakpoint matches in the

corresponding breakpoint-address registers (DR0 through DR3). The processor

asserts then deasserts the corresponding BPi# pin when a breakpoint match

occurs. When a PBi flag is clear, the performance monitoring/breakpoint pins

report performance events. Processor execution is not affected by reporting

performance events.

• TR (trace message enable) flag (bit 6) — When set, trace messages are

enabled as described in Section 16.4.4, “Branch Trace Messages.” Setting this

flag greatly reduces the performance of the processor. When trace messages are

enabled, the values stored in the LastBranchToIP, LastBranchFromIP, LastExcep-

tionToIP, and LastExceptionFromIP MSRs are undefined.

16.10.2 Last Branch and Last Exception MSRs

The LastBranchToIP and LastBranchFromIP MSRs are 32-bit registers for recording

the instruction pointers for the last branch, interrupt, or exception that the processor

took prior to a debug exception being generated. When a branch occurs, the

processor loads the address of the branch instruction into the LastBranchFromIP MSR

and loads the target address for the branch into the LastBranchToIP MSR.

When an interrupt or exception occurs (other than a debug exception), the address

of the instruction that was interrupted by the exception or interrupt is loaded into the

LastBranchFromIP MSR and the address of the exception or interrupt handler that is

called is loaded into the LastBranchToIP MSR.

The LastExceptionToIP and LastExceptionFromIP MSRs (also 32-bit registers) record

the instruction pointers for the last branch that the processor took prior to an excep-

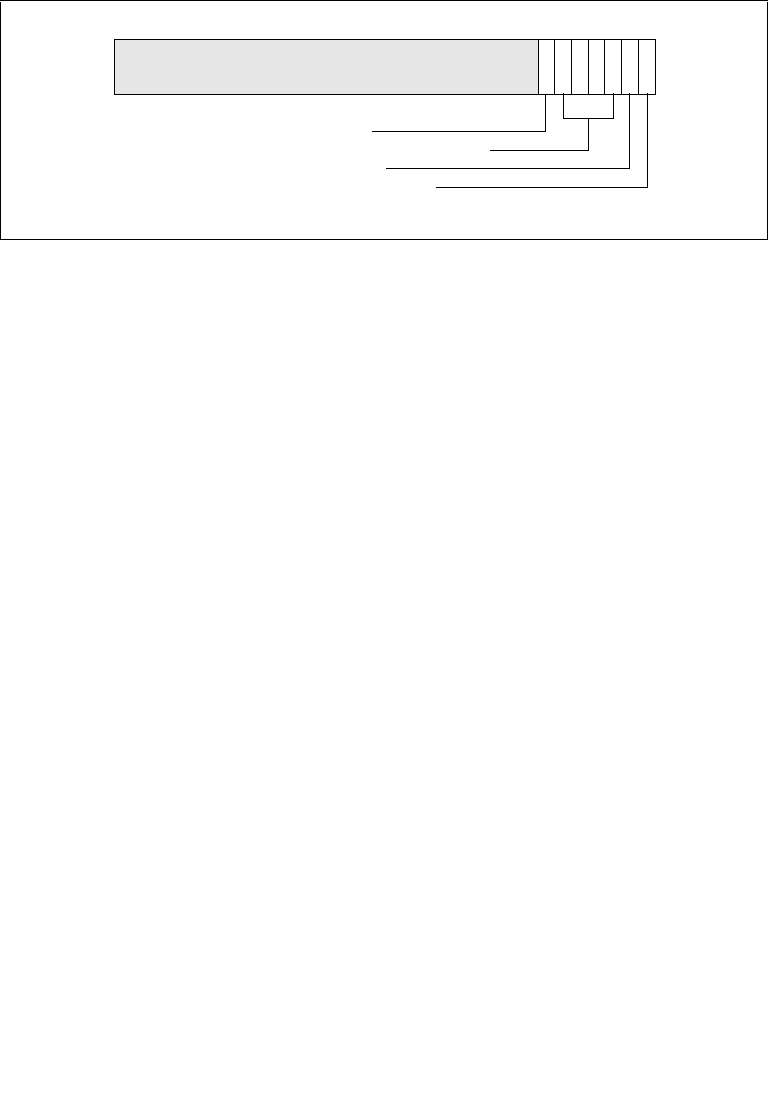

Figure 16-18. DEBUGCTLMSR Register (P6 Family Processors)

31

TR — Trace messages enable

PBi — Performance monitoring/breakpoint pins

BTF — Single-step on branches

LBR — Last branch/interrupt/exception

76

543

2

1

0

P

B

2

P

B

1

P

B

0

B

T

F

T

R

L

B

R

P

B

3

Reserved