Vol. 3 6-21

INTERRUPT AND EXCEPTION HANDLING

6.13 ERROR CODE

When an exception condition is related to a specific segment, the processor pushes

an error code onto the stack of the exception handler (whether it is a procedure or

task). The error code has the format shown in

Figure 6-6. The error code resembles

a segment selector; however, instead of a TI flag and RPL field, the error code

contains 3 flags:

EXT External event (bit 0) — When set, indicates that an event external

to the program, such as a hardware interrupt, caused the exception.

IDT Descriptor location (bit 1) — When set, indicates that the index

portion of the error code refers to a gate descriptor in the IDT; when

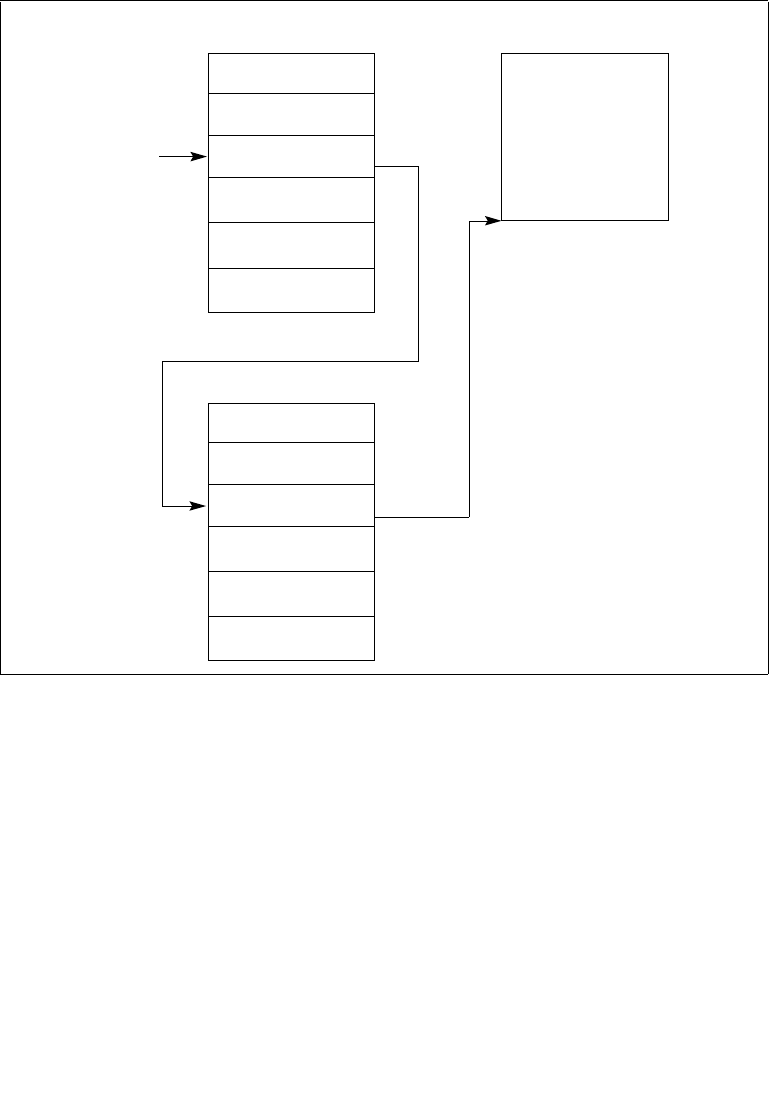

Figure 6-5. Interrupt Task Switch

IDT

Task Gate

TSS for Interrupt-

TSS Selector

GDT

TSS Descriptor

Interrupt

Vector

TSS

Base

Address

Handling Task