Vol. 3 16-19

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

16.4.8 LBR Stack

The last branch record stack and top-of-stack (TOS) pointer MSRs are supported

across Intel 64 and IA-32 processor families. However, the number of MSRs in the

LBR stack and the valid range of TOS pointer value can vary between different

processor families. Table 16-3 lists the LBR stack size and TOS pointer range for

several processor families according to the CPUID signatures of Display-

Family/DisplayModel encoding (see CPUID instruction in Chapter 3 of Intel® 64 and

IA-32 Architectures Software Developer’s Manual, Volume 2A).

The last branch recording mechanism tracks not only branch instructions (like JMP,

Jcc, LOOP and CALL instructions), but also other operations that cause a change in

the instruction pointer (like external interrupts, traps and faults). The branch

recording mechanisms generally employs a set of MSRs, referred to as last branch

record (LRB) stack. The size and exact locations of the LRB stack are generally

model-specific.

• Last Branch Record (LBR) Stack — The LBR consists of N pairs of MSRs (N is

listed in the LBR stack size column of Table 16-3) that store source and

destination address of recent branches (see Figure 16-3):

— MSR_LASTBRANCH_0_FROM_IP (address is model specific) through the next

consecutive (N-1) MSR address store source addresses

— MSR_LASTBRANCH_0_TO_IP (address is model specific ) through the next

consecutive (N-1) MSR address store destination addresses.

• Last Branch Record Top-of-Stack (TOS) Pointer — The lowest significant M

bits of the TOS Pointer MSR (MSR_LASTBRANCH_TOS, address is model specific)

contains an M-bit pointer to the MSR in the LBR stack that contains the most

recent branch, interrupt, or exception recorded. The valid range of the M-bit POS

pointer is given in Table 16-3.

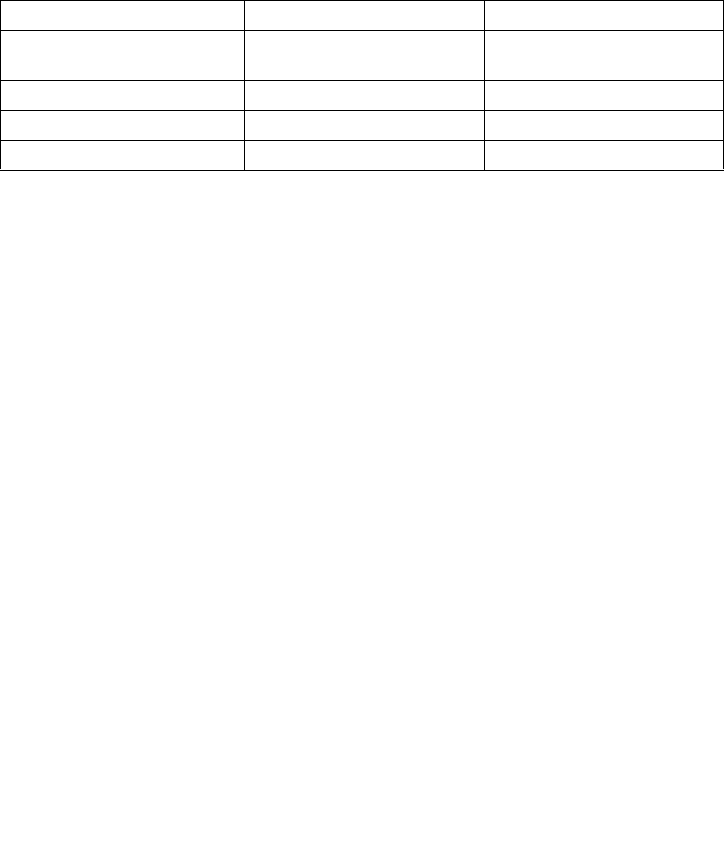

Table 16-3. LBR Stack Size and TOS Pointer Range

DisplayFamily_DisplayModel Size of LBR Stack Range of TOS Pointer

06_1AH, 06_1EH, 06_1FH,

06_2EH

16 0 to 15

06_17H, 06_1DH 40 to 3

06_0FH 40 to 3

06_1CH 80 to 7