Vol. 3 10-43

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

Self Invalid X Lowest Priority, NMI, INIT, SMI, Start-

Up

X

All Including Self Valid Edge Fixed X

All Including Self Invalid

2

Level Fixed X

All Including Self Invalid X Lowest Priority, NMI, INIT, SMI, Start-

Up

X

All Excluding

Self

Valid Edge Fixed, Lowest Priority

1

,

4

, NMI, INIT,

SMI, Start-Up

X

All Excluding

Self

Invalid

2

Level FIxed, Lowest Priority

4

, NMI, INIT,

SMI, Start-Up

X

NOTES:

1. The ability of a processor to send a lowest priority IPI is model specific.

2. For these interrupts, if the trigger mode bit is 1 (Level), the local xAPIC will override the bit set-

ting and issue the interrupt as an edge triggered interrupt.

3. X means the setting is ignored.

4. When using the “lowest priority” delivery mode and the “all excluding self” destination, the IPI

can be redirected back to the issuing APIC, which is essentially the same as the “all including

self” destination mode.

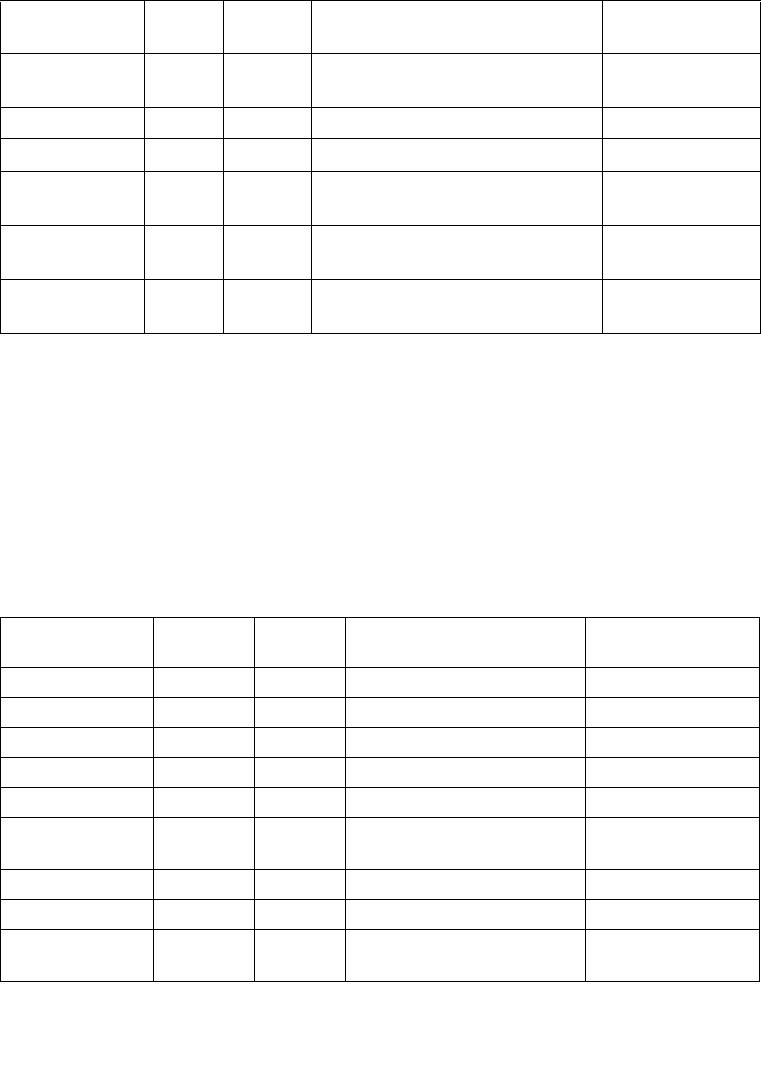

Table 10-7 Valid Combinations for the P6 Family Processors’

Local APIC Interrupt Command Register

Destination

Shorthand

Valid/

Invalid

Trigger

Mode

Delivery Mode

Destination Mode

No Shorthand Valid Edge All Modes

1

Physical or Logical

No Shorthand Valid

2

Level Fixed, Lowest Priority

1

, NMI Physical or Logical

No Shorthand Valid

3

Level INIT Physical or Logical

Self Valid Edge Fixed X

4

Self 1 Level Fixed X

Self Invalid

5

X Lowest Priority, NMI, INIT,

SMI, Start-Up

X

All including Self Valid Edge Fixed X

All including Self Valid

2

Level Fixed X

All including Self Invalid

5

X Lowest Priority, NMI, INIT,

SMI, Start-Up

X

Table 10-6 Valid Combinations for the Pentium 4 and Intel Xeon Processors’

Local xAPIC Interrupt Command Register (Contd.)

Destination

Shorthand

Valid/

Invalid

Trigger

Mode

Delivery Mode

Destination

Mode