15-4 Vol. 3

MACHINE-CHECK ARCHITECTURE

Where:

• Count field, bits 7:0 — Indicates the number of hardware unit error-reporting

banks available in a particular processor implementation.

• MCG_CTL_P (control MSR present) flag, bit 8 — Indicates that the processor

implements the IA32_MCG_CTL MSR when set; this register is absent when clear.

• MCG_EXT_P (extended MSRs present) flag, bit 9 — Indicates that the

processor implements the extended machine-check state registers found starting

at MSR address 180H; these registers are absent when clear.

• MCG_CMCI_P (Corrected MC error counting/signaling extension

present) flag, bit 10 — Indicates (when set) that extended state and

associated MSRs necessary to support the reporting of an interrupt on a

corrected MC error event and/or count threshold of corrected MC errors, is

present. When this bit is set, it does not imply this feature is supported across all

banks. Software should check the availability of the necessary logic on a bank by

bank basis when using this signaling capability (i.e. bit 30 settable in individual

IA32_MCi_CTL2 register).

• MCG_TES_P (threshold-based error status present) flag, bit 11 —

Indicates (when set) that bits 56:53 of the IA32_MCi_STATUS MSR are part of

the architectural space. Bits 56:55 are reserved, and bits 54:53 are used to

report threshold-based error status. Note that when MCG_TES_P is not set, bits

56:53 of the IA32_MCi_STATUS MSR are model-specific.

• MCG_EXT_CNT, bits 23:16 — Indicates the number of extended machine-

check state registers present. This field is meaningful only when the MCG_EXT_P

flag is set.

• MCG_SER_P (software error recovery support present) flag, bit 24—

Indicates (when set) that the processor supports software error recovery (see

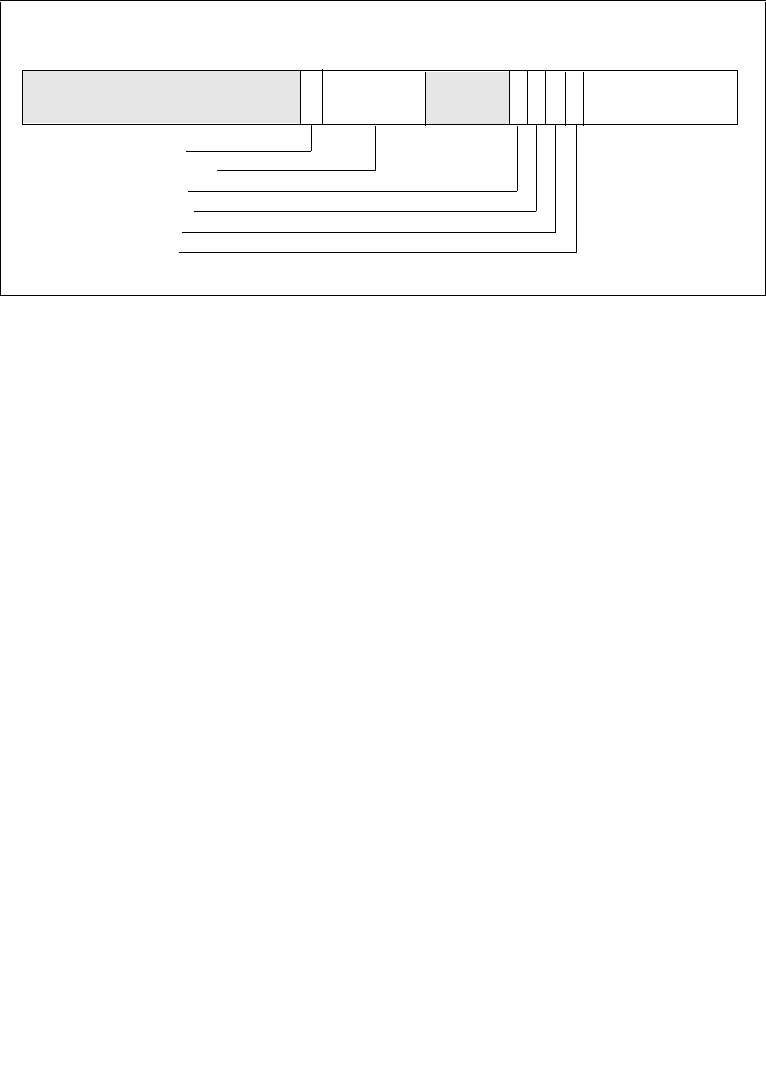

Figure 15-2. IA32_MCG_CAP Register

MCG_TES_P[11]

MCG_EXT_CNT[23:16]

63

9

Reserved

101112

MCG_CMCI_P[10]

0

87

Count

MCG_EXT_P[9]

15162324

MCG_CTL_P[8]

MCG_SER_P[24]

25