11-38 Vol. 3

MEMORY CACHE CONTROL

Before attempting to access these SMRR registers, software must test bit 11 in the

IA32_MTRRCAP register. If SMRR is not supported, reads from or writes to registers

cause general-protection exceptions.

When the valid flag in the IA32_SMRR_PHYSMASK MSR is 1, accesses to the specified

address range are treated as follows:

• If the logical processor is in SMM, accesses uses the memory type in the

IA32_SMRR_PHYSBASE MSR.

• If the logical processor is not in SMM, write accesses are ignored and read

accesses return a fixed value for each byte. The uncacheable memory type (UC)

is used in this case.

The above items apply even if the address range specified overlaps with a range

specified by the MTRRs.

11.11.3 Example Base and Mask Calculations

The examples in this section apply to processors that support a maximum physical

address size of 36 bits. The base and mask values entered in variable-range MTRR

pairs are 24-bit values that the processor extends to 36-bits.

For example, to enter a base address of 2 MBytes (200000H) in the

IA32_MTRR_PHYSBASE3 register, the 12 least-significant bits are truncated and the

value 000200H is entered in the PhysBase field. The same operation must be

performed on mask values. For example, to map the address range from 200000H to

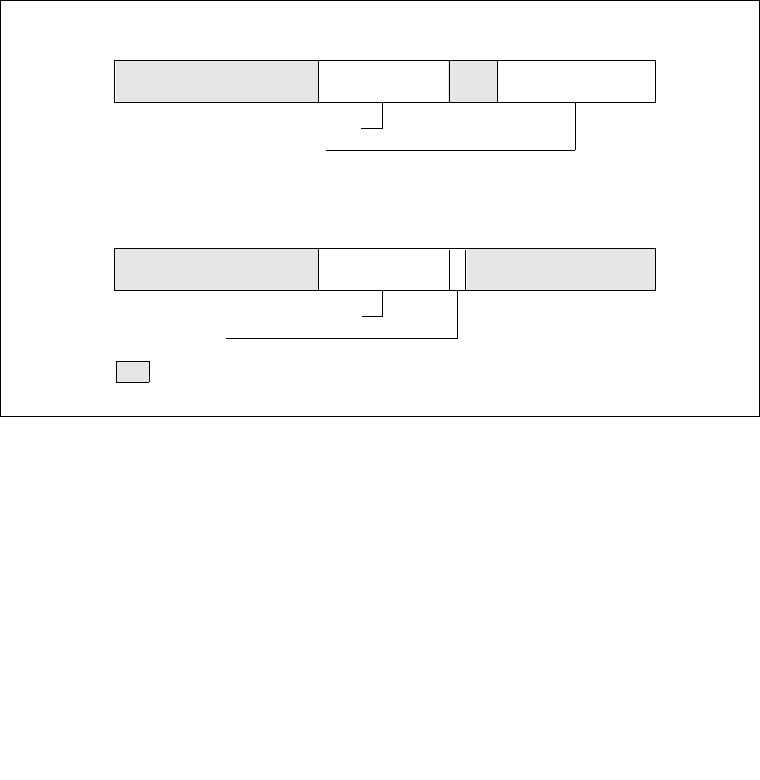

Figure 11-8. IA32_SMRR_PHYSBASE and IA32_SMRR_PHYSMASK SMRR Pair

V — Valid

PhysMask — Sets range mask

IA32_SMRR_PHYSMASK Register

63

0

Reserved

101112

V

Reserved

31

PhysMask

Type — Memory type for range

PhysBase — Base address of range

IA32_SMRR_PHYSBASE Register

63

0

Reserved

1112

Type

31

PhysBase

78

Reserved