Vol. 3 16-9

DEBUGGING, PROFILING BRANCHES AND TIME-STAMP COUNTER

16.3 DEBUG EXCEPTIONS

The Intel 64 and IA-32 architectures dedicate two interrupt vectors to handling

debug exceptions: vector 1 (debug exception, #DB) and vector 3 (breakpoint excep-

tion, #BP). The following sections describe how these exceptions are generated and

typical exception handler operations.

16.3.1 Debug Exception (#DB)—Interrupt Vector 1

The debug-exception handler is usually a debugger program or part of a larger soft-

ware system. The processor generates a debug exception for any of several condi-

tions. The debugger checks flags in the DR6 and DR7 registers to determine which

condition caused the exception and which other conditions might apply. Table 16-2

shows the states of these flags following the generation of each kind of breakpoint

condition.

Instruction-breakpoint and general-detect condition (see Section 16.3.1.3, “General-

Detect Exception Condition”) result in faults; other debug-exception conditions result

in traps. The debug exception may report one or both at one time. The following

sections describe each class of debug exception.

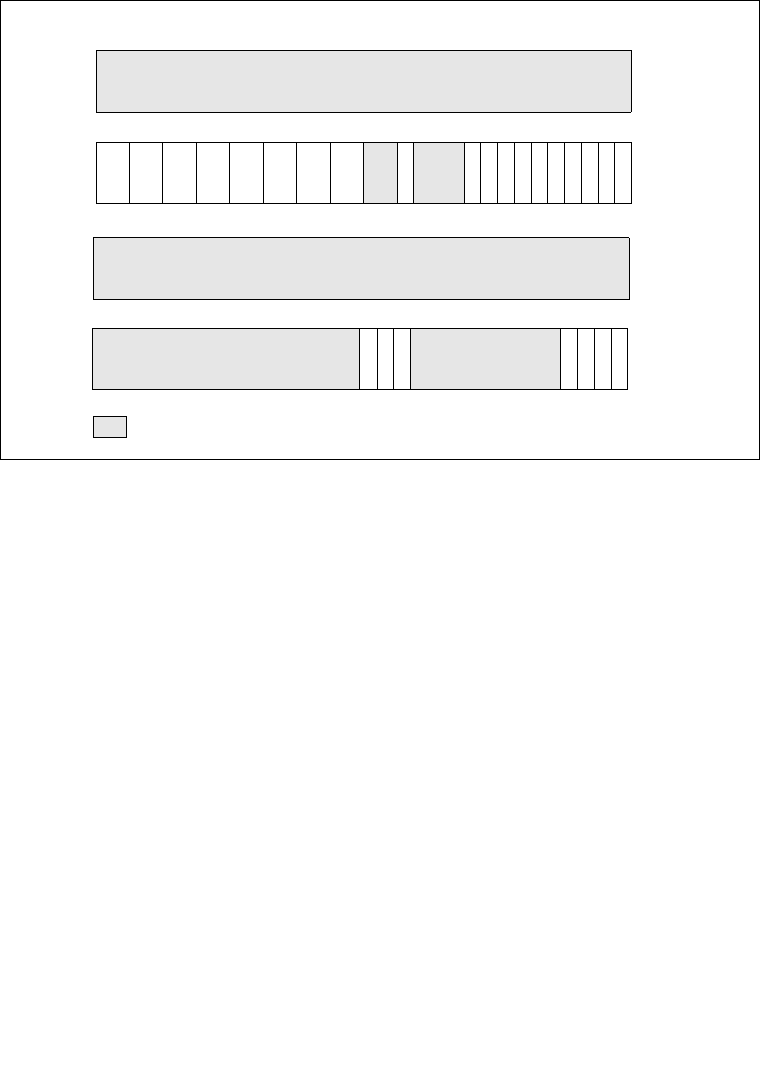

Figure 16-2. DR6/DR7 Layout on Processors Supporting Intel 64 Technology

31

24

23

22

21 20 19 16

15

13

14 12 11

8

7

0

DR7

L

Reserved

0

123456

910

1718

252627282930

G

0

L

1

L

2

L

3

G

3

L

E

G

E

G

2

G

1

G

D

R/W

0

LEN

0

R/W

1

LEN

1

R/W

2

LEN

2

R/W

3

LEN

3

31

16

15

13

14 12

11

8

7

0

DR6

B

0

123456

910

B

1

B

2

B

3

0111111111

B

D

B

S

B

T

63

32

63

32

DR6

DR7

00

001

Reserved (set to 1)