8-34 Vol. 3

MULTIPLE-PROCESSOR MANAGEMENT

during power-up and initialization is 8 bits. Bits 2:1 form a 2-bit physical package

identifier (which can also be thought of as a socket identifier). In systems that

configure physical processors in clusters, bits 4:3 form a 2-bit cluster ID. Bit 0 is used

in the Intel Xeon processor MP to identify the two logical processors within the

package (see

Section 8.9.3, “Hierarchical ID of Logical Processors in an MP System”).

For Intel Xeon processors that do not support Intel Hyper-Threading Technology, bit

0 is always set to 0; for Intel Xeon processors supporting Intel Hyper-Threading

Technology, bit 0 performs the same function as it does for Intel Xeon processor MP.

For more recent multi-core processors, see Section 8.9.1, “Hierarchical Mapping of

Shared Resources” for a complete description of the topological relationships

between logical processors and bit field locations within an initial APIC ID across Intel

64 and IA-32 processor families.

Note the number of bit fields and the width of bit-fields are dependent on processor

and platform hardware capabilities. Software should determine these at runtime.

When initial APIC IDs are assigned to logical processors, the value of APIC ID

assigned to a logical processor will respect the bit-field boundaries corresponding

core, physical package, etc. Additional examples of the bit fields in the initial APIC ID

of multi-threading capable systems are shown in

Section 8.9.

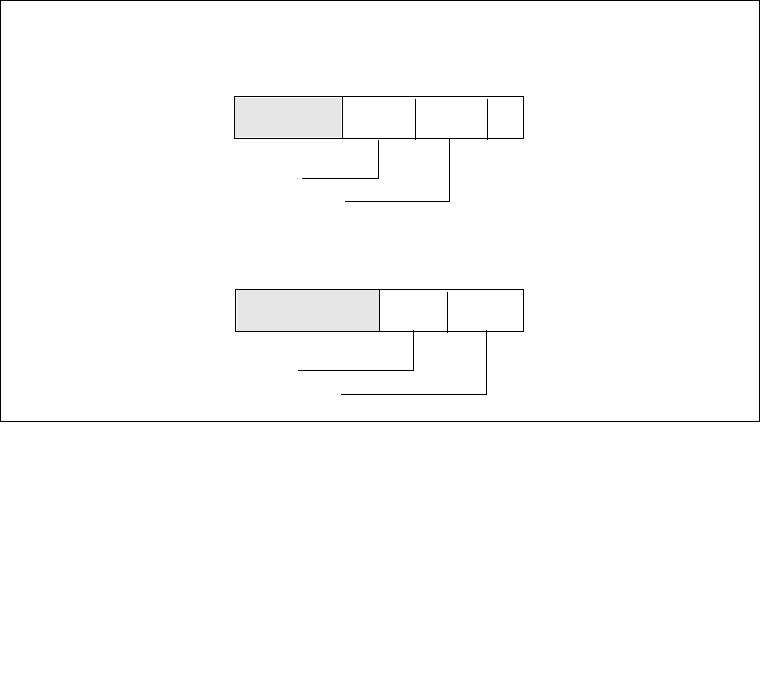

For P6 family processors, the APIC ID that is assigned to a processor during power-

up and initialization is 4 bits (see

Figure 8-2). Here, bits 0 and 1 form a 2-bit

processor (or socket) identifier and bits 2 and 3 form a 2-bit cluster ID.

Figure 8-2. Interpretation of APIC ID in Early MP Systems

0

Processor ID

17 432

Cluster

Reserved

0

Processor ID

17 4325

Cluster

Reserved

APIC ID Format for Intel Xeon Processors that

APIC ID Format for P6 Family Processors

0

do not Support Intel Hyper-Threading Technology