11-18 Vol. 3

MEMORY CACHE CONTROL

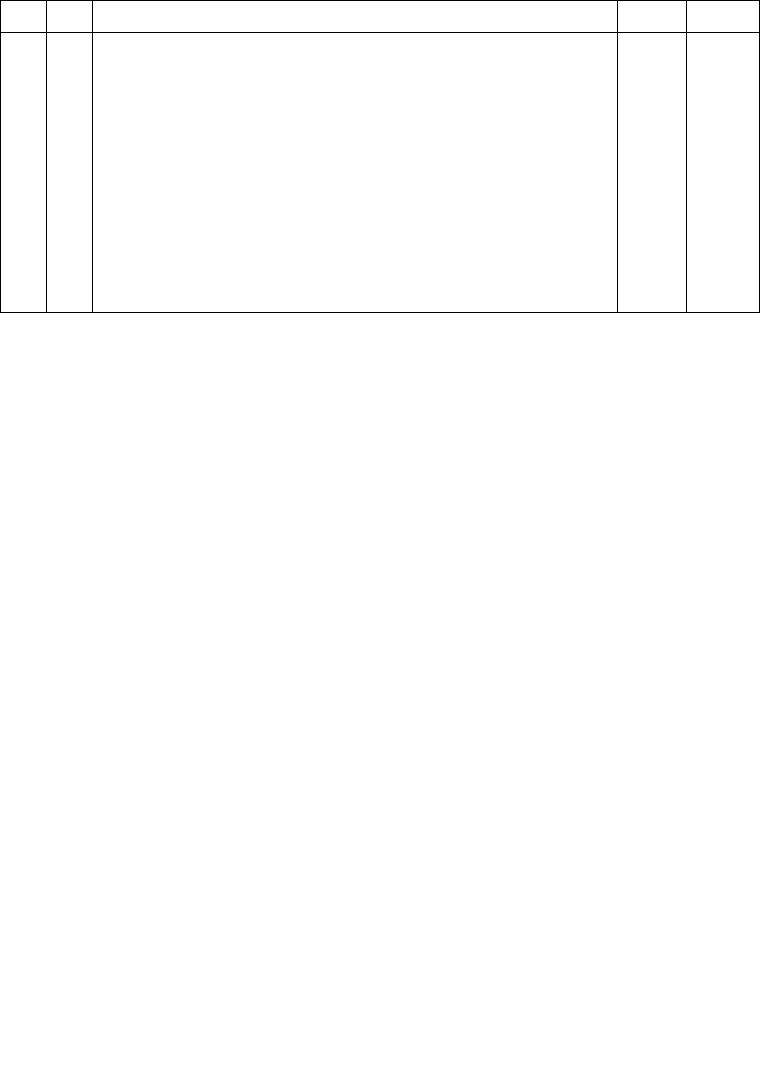

• NW flag, bit 29 of control register CR0 — Controls the write policy for system

memory locations (see Section 2.5, “Control Registers”). If the NW and CD flags

are clear, write-back is enabled for the whole of system memory, but may be

restricted for individual pages or regions of memory by other cache-control

mechanisms. Table 11-5 shows how the other combinations of CD and NW flags

affects caching.

NOTES

For the Pentium 4 and Intel Xeon processors, the NW flag is a don’t

care flag; that is, when the CD flag is set, the processor uses the no-

fill cache mode, regardless of the setting of the NW flag.

For Intel Atom processors, the NW flag is a don’t care flag; that is,

when the CD flag is set, the processor disables caching, regardless of

the setting of the NW flag.

For the Pentium processor, when the L1 cache is disabled (the CD and

NW flags in control register CR0 are set), external snoops are

accepted in DP (dual-processor) systems and inhibited in unipro

-

cessor systems.

When snoops are inhibited, address parity is not checked and

APCHK# is not asserted for a corrupt address; however, when snoops

are accepted, address parity is checked and APCHK# is asserted for

1 1 Memory coherency is not maintained.

2, 3

• (P6 family and Pentium processors.) State of the processor after

a power up or reset.

• Read hits access the cache; read misses do not cause

replacement.

• Write hits update the cache and change exclusive lines to

modified.

Yes

Yes

Yes

Yes

Yes

Yes

• Shared lines remain shared after write hit.

• Write misses access memory.

• Invalidation is inhibited when snooping; but is allowed with INVD

and WBINVD instructions.

• External snoop traffic is supported.

Yes

Yes

Yes

No

Yes

Yes

Yes

Yes

NOTES:

1. The L2/L3 column in this table is definitive for the Pentium 4, Intel Xeon, and P6 family proces-

sors. It is intended to represent what could be implemented in a system based on a Pentium pro-

cessor with an external, platform specific, write-back L2 cache.

2. The Pentium 4 and more recent processor families do not support this mode; setting the CD and

NW bits to 1 selects the no-fill cache mode.

3. Not supported In Intel Atom processors. If CD = 1 in an Intel Atom processor, caching is disabled.

Table 11-5. Cache Operating Modes

CD NW Caching and Read/Write Policy L1 L2/L3

1