Vol. 3 14-21

POWER AND THERMAL MANAGEMENT

• Reading Valid (bit 31, RO) — Indicates if the digital readout in bits 22:16 is

valid. The readout is valid if bit 31 = 1.

Changes to temperature can be detected using two thresholds (see Figure 14-12);

one is set above and the other below the current temperature. These thresholds have

the capability of generating interrupts using the core's local APIC which software

must then service. Note that the local APIC entries used by these thresholds are also

used by the Intel

®

Thermal Monitor; it is up to software to determine the source of a

specific interrupt.

See Figure 14-12 for the layout of IA32_THERM_INTERRUPT MSR. Bit fields include:

• High-Temperature Interrupt Enable (bit 0, R/W) — This bit allows the BIOS

to enable the generation of an interrupt on the transition from low-temperature

to a high-temperature threshold. Bit

0 = 0 (default) disables interrupts;

bit

0 = 1 enables interrupts.

• Low-Temperature Interrupt Enable (bit 1, R/W) — This bit allows the BIOS

to enable the generation of an interrupt on the transition from high-temperature

to a low-temperature (TCC de-activation). Bit

1 = 0 (default) disables interrupts;

bit

1 = 1 enables interrupts.

• PROCHOT# Interrupt Enable (bit 2, R/W) — This bit allows the BIOS or OS

to enable the generation of an interrupt when PROCHOT# has been asserted by

another agent on the platform and the Bidirectional Prochot feature is enabled.

Bit 2 = 0 disables the interrupt; bit 2 = 1 enables the interrupt.

• FORCEPR# Interrupt Enable (bit 3, R/W) — This bit allows the BIOS or OS to

enable the generation of an interrupt when FORCEPR# has been asserted by

another agent on the platform. Bit 3 = 0 disables the interrupt; bit 3 = 1 enables

the interrupt.

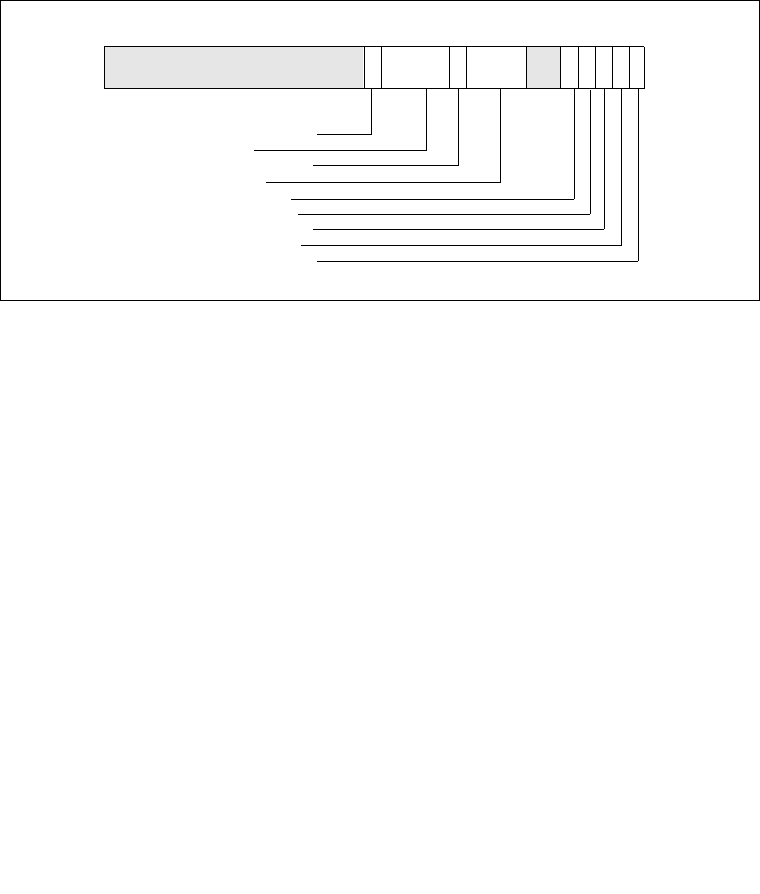

Figure 14-12. IA32_THERM_INTERRUPT Register

63 0

Reserved

15

Threshold #2 Interrupt Enable

1234581416222324

Threshold #2 Value

Threshold #1 Interrupt Enable

Threshold #1 Value

Overheat Interrupt Enable

FORCPR# Interrupt Enable

PROCHOT# Interrupt Enable

Low Temp. Interrupt Enable

High Temp. Interrupt Enable