Vol. 3 4-33

PAGING

— Data reads.

Data may be read from any linear address with a valid translation for which

the U/S flag (bit 2) is 1 in every paging-structure entry controlling the trans-

lation.

— Data writes.

Data may be written to any linear address with a valid translation for which

6

3

6

2

6

1

6

0

5

9

5

8

5

7

5

6

5

5

5

4

5

3

5

2

5

1

M

1

M-1

3

2

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

09876543210

Reserved

2

Address of PML4 table Ignored

P

C

D

P

W

T

Ign. CR3

X

D

Ignored Rsvd. Address of page-directory-pointer table Ign.

R

s

v

d

I

g

n

A

P

C

D

P

W

T

U

/

S

R

/

W

1

PML4E:

present

Ignored 0

PML4E:

not

present

X

D

Ignored Rsvd. Address of page directory Ign.

R

s

v

d

I

g

n

A

P

C

D

P

W

T

U

/

S

R

/

W

1

PDPTE:

present

Ignored 0

PDTPE:

not

present

X

D

Ignored Rsvd.

Address of

2MB page frame

Reserved

P

A

T

Ign. G 1

DA

P

C

D

P

W

T

U

/

S

R

/

W

1

PDE:

2MB

page

X

D

Ignored Rsvd. Address of page table Ign. 0

I

g

n

A

P

C

D

P

W

T

U

/

S

R

/

W

1

PDE:

page

table

Ignored 0

PDE:

not

present

X

D

Ignored Rsvd. Address of 4KB page frame Ign. G

P

A

T

DA

P

C

D

P

W

T

U

/

S

R

/

W

1

PTE:

4KB

page

Ignored 0

PTE:

not

present

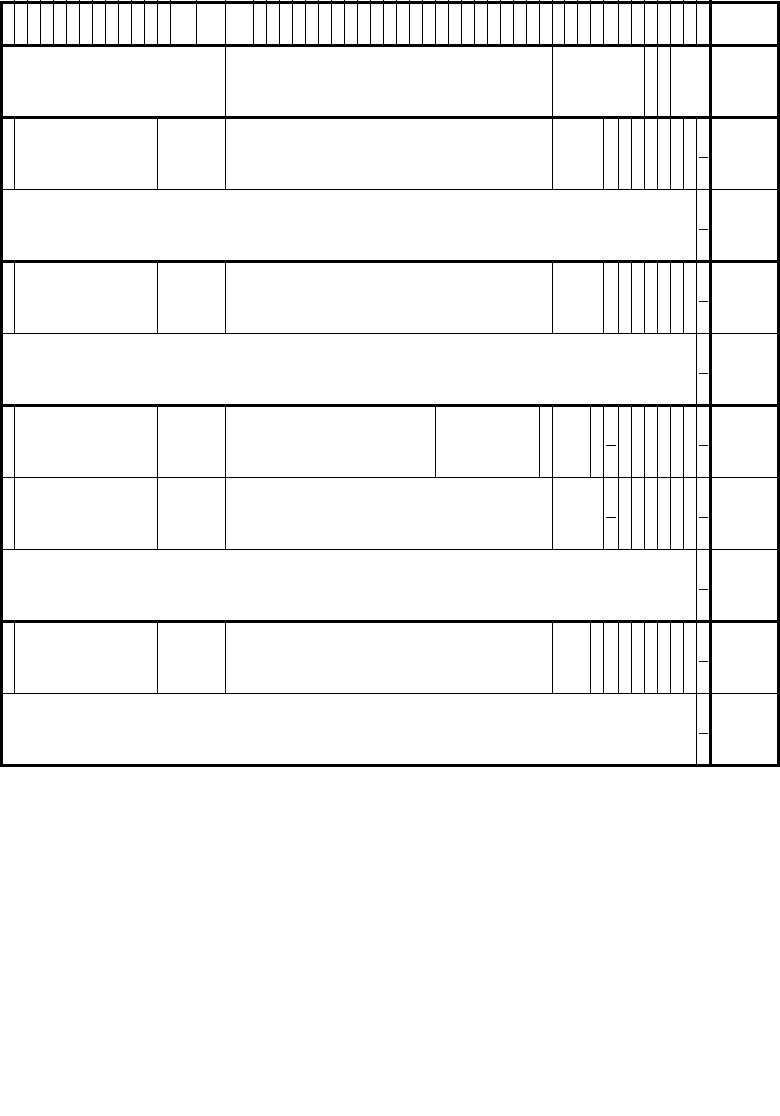

Figure 4-10. Formats of CR3 and Paging-Structure Entries with IA-32e Paging

NOTES:

1. M is an abbreviation for MAXPHYADDR.

2. Reserved fields must be 0.