. . . . .

WORKING WITH THE CPU

MemoryManagement Unit (MMU)

www.digiembedded.com 117

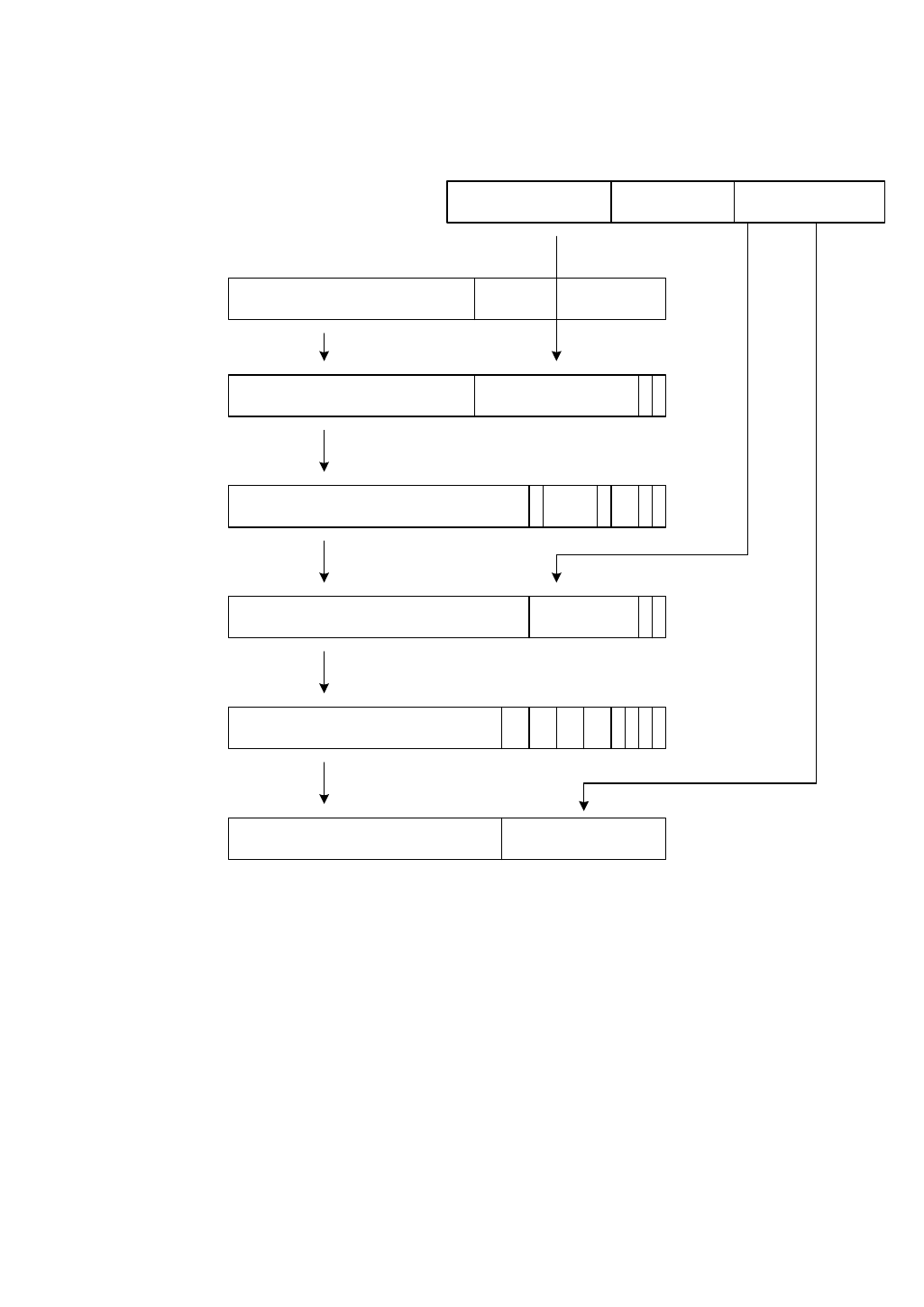

Translating

sequence for small

page references

If a small page descriptor is included in a fine page table, the upper two bits of the

page index and low-order two bits of the fine page table index overlap. Each fine

page table entry for a small page must be duplicated four times.

31 14 13 0

Translation base

1

Translation table base

31 1413 0

Translation base

2

Table index 0 0

31 2019 0

Table index Page index

First-level descriptor

31 0

Coarse page table base address

2

01

1345

Domain 1

31 0

Coarse page table base address

Level two

table index

1211

Modified virtual address

8910

12910

31 1211109876543210

00L2 table index

01BCAP0AP1AP2AP3Page base address

Page base address

31 01211

Page index

Physical address

Second-level descriptor