. . . . .

I2C MASTER/SLAVE INTERFACE

Status Receive Data register

www.digiembedded.com 451

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Receive Data register

Address: 9005 0000

The Status Receive Data register (

STATUS_RX_DATA_REG) is the primary interface

register for receipt of data between the I/O hub and I

2

C bus. This register is read

only.

Register

Register bit

assignment

Bits Access Mnemonic Reset Description

D31:16 N/A Reserved N/A N/A

D15 W PIPE 0x0 Pipeline mode

Must be set to 0.

D14 W DLEN 0x0 I

2

C DLEN port (iic_dlen)

Must be set to 0.

D13 W TXVAL 0x0 Provide new transmit data in

CMD_TX_DATA_REG (tx_data_val).

D12:08 W CMD 0x0 Command to be sent (see "Master module and

slave module commands," beginning on page

449)

D07:00 W TXDATA 0x0 Transmit data to I

2

C bus.

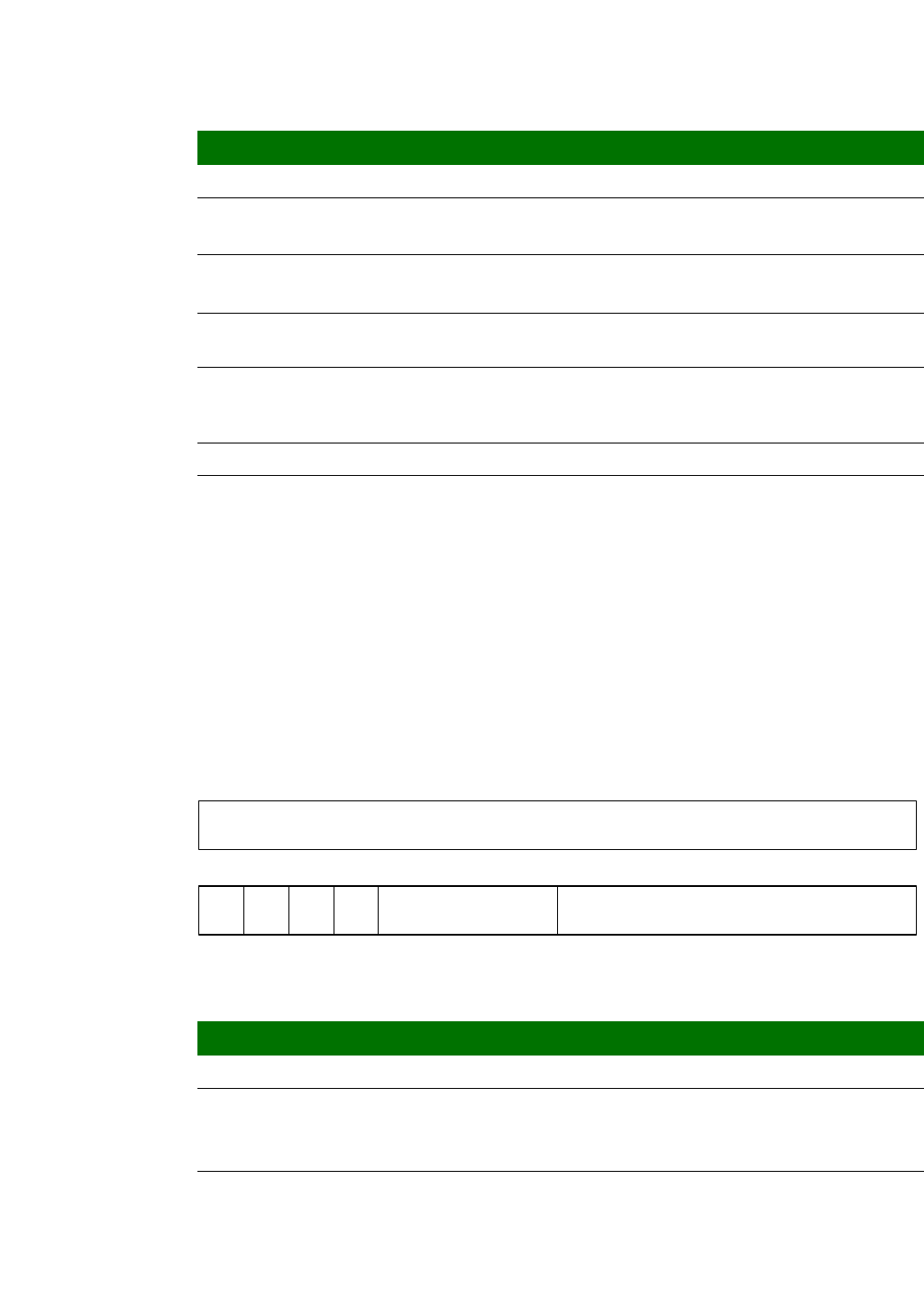

SCMDL

MCMDL

IRQCD RXDATA

13121110987654321015

14

BSTS RDE

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Bits Access Mnemonic Reset Description

D31:16 N/A Reserved N/A N/A

D15 R BSTS N/A Bus status (master only)

0Bus is free

1Bus is occupied

D14 R RDE N/A Receive data enable (

rx_data_en)

Received data is available.