. . . . .

MEMORY CONTROLLER

Static memory controller

www.digiembedded.com 207

2 When the power-on reset (reset_n) goes inactive, the processor starts booting

from

0x00000000 in memory.

3 The software programs the optimum delay values in flash memory so the boot

code can run at full speed.

4 The code branches to chip select 1 so the code can continue executing from the

non-remapped memory location.

5 The appropriate values are programmed into the memory controller to

configure chip select 4, and the memory device is initialized.

6 The address mirroring is disabled by clearing the address mirror (M) field in the

Control register.

7 The ARM reset and interrupt vectors are copied from flash memory to SDRAM

that can then be accessed at address

0x00000000.

8 More boot, initialization, or application code is executed.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Static memory controller

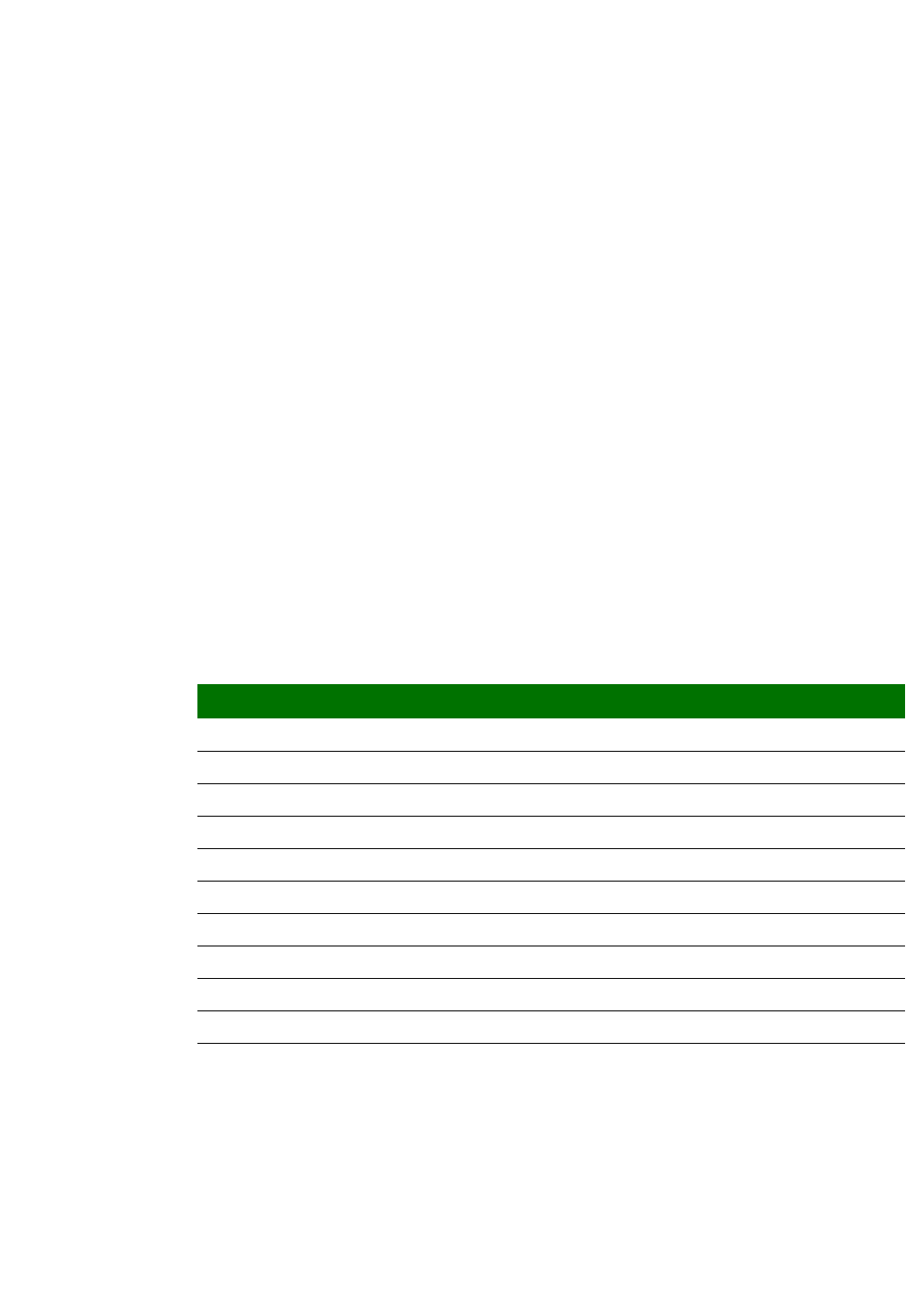

This table shows configurations for the static memory controller with different

types of memory devices. See “StaticMemory Configuration 0–3 registers” on

page 251 for more information.

Device Write protect Page mode Buffer

ROM Enabled Disabled Disabled

a

Page mode ROM Enabled Enabled Enabled

a

Extended wait ROM Enabled Disabled Disabled

a

SRAM Disabled (or enabled)

b

Disabled Disabled

a

Page mode SRAM Disabled (or enabled)

b

Enabled Enabled

a

Extended wait SRAM Disabled (or enabled)

b

Disabled Disabled

a

Flash Disabled or (enabled)

b

Disabled Disabled

c

Page mode flash Disabled or (enabled)

b

Enabled Enabled

c

Extended wait flash Disabled or (enabled)

b

Disabled Disabled

a

Memory mapped peripheral Disabled (or enabled)

b

Disabled Disabled

a Enabling the buffers means that any access causes the buffer to be used. Depending on the

application, this can provide performance improvements. Devices without async-page-mode

support generally work better with the buffer disabled. Again, depending on the application, this

can provide performance improvements.

b SRAM and Flash memory devices can be write-protected if required.

c Buffering must be disabled when performing Flash memory commands and during writes.