. . . . .

ETHERNET COMMUNICATION MODULE

Ethernet Interrupt Enable register

www.digiembedded.com 319

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Interrupt Enable register

Address: A060 0A14

The Ethernet Interrupt Enable register contains individual enable bits for each of

the bits in the Ethernet Interrupt Status register. When these bits are cleared, the

corresponding bit in the Ethernet Interrupt Status register cannot cause the

interrupt signal to the system to be asserted when it is set.

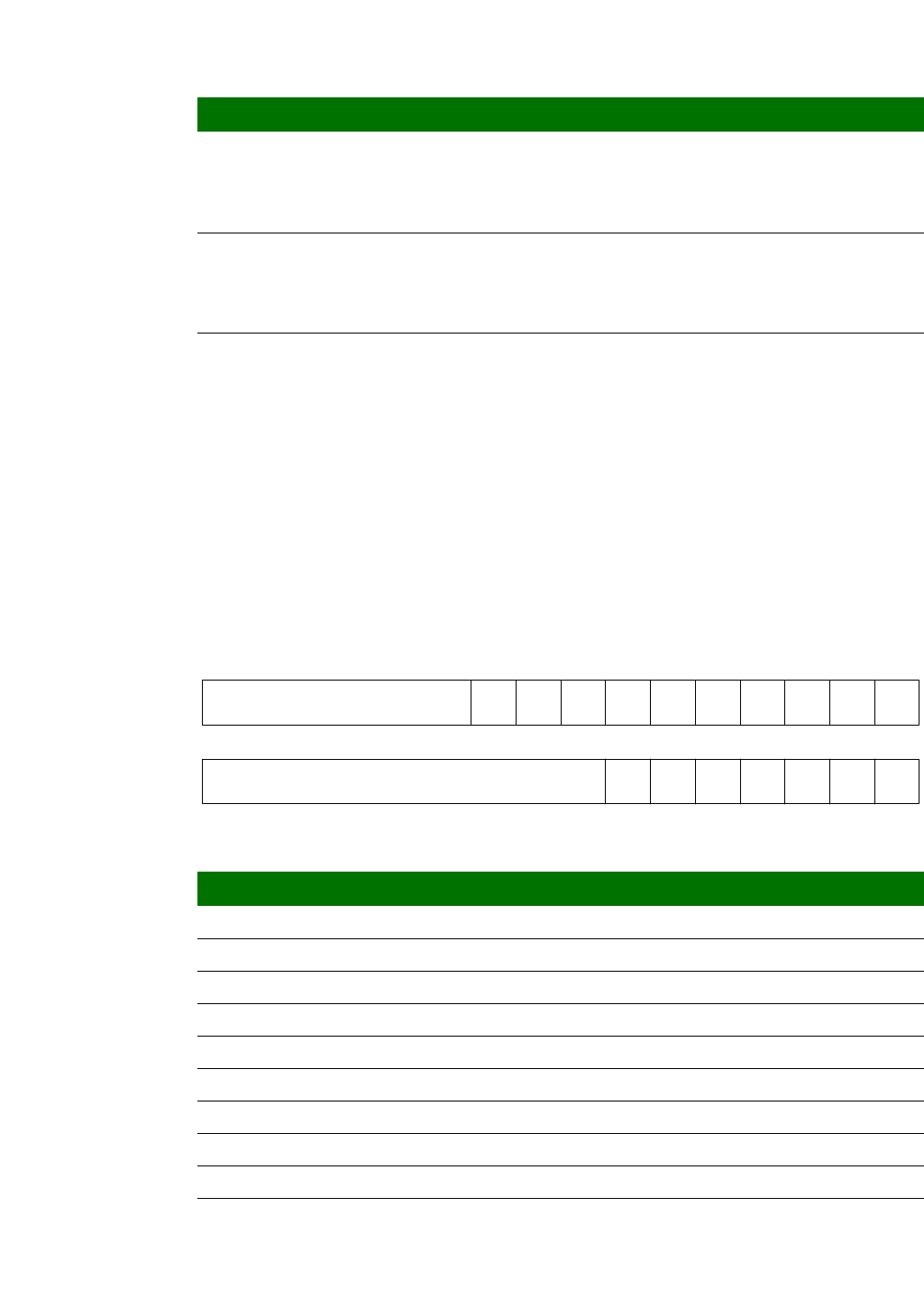

Register

Register bit

assignment

D01 R/C TXERR 0 Last frame not transmitted successfully.

Assigned to TX interrupt. See “Ethernet Interrupt

Status register” on page 317 for information about

restarting the transmitter when this bit is set.

D00 R/C TXIDLE 0

TX_WR logic has no frame to transmit.

Assigned to TX interrupt. See “Ethernet Interrupt

Status register” on page 317 for information about

restarting the transmitter when this bit is set.

Bits Access Mnemonic Reset Description

Reserved

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

EN_RX

DONE

C

EN_RX

DONE

D

EN_

RXNO

BUF

EN_RX

BUF

FUL

EN_

RXBR

EN_RX

OVFL_

DATA

EN_RX

OVFL_

STAT

EN_

RX

BUFC

EN_RX

DONE

A

EN_RX

DONE

B

EN_ST

OVFL

Not

used

EN_TX

BUFC

EN_TX

BUF

NR

EN_

TX

DONE

EN_

TX

ERR

EN_

TX

IDLE

Bits Access Mnemonic Reset Description

D31:26 N/A Reserved N/A N/A

D25 R/W

EN_RXOVFL_DATA

0 Enable the RXOVFL_DATA interrupt bit.

D24 R/W

EN_RXOVFL_STAT

0 Enable the RXOVFL_STATUS interrupt bit.

D23 R/W EN_RXBUFC 0 Enable the RXBUFC interrupt bit.

D22 R/W EN_RXDONEA 0 Enable the RXDONEA interrupt bit.

D21 R/W EN_RXDONEB 0 Enable the RXDONEB interrupt bit.

D20 R/W EN_RXDONEC 0 Enable the RXDONEC interrupt bit.

D19 R/W EN_RXDONED 0 Enable the RXDONED interrupt bit.

D18 R/W EN_RXNOBUF 0 Enable the RXNOBUF interrupt bit.

D17 R/W EN_RXBUFFUL 0 Enable the RXBUFFUL interrupt bit.