SERIAL CONTROL MODULE: UART

Interrupt Status register

396 Hardware Reference NS9215

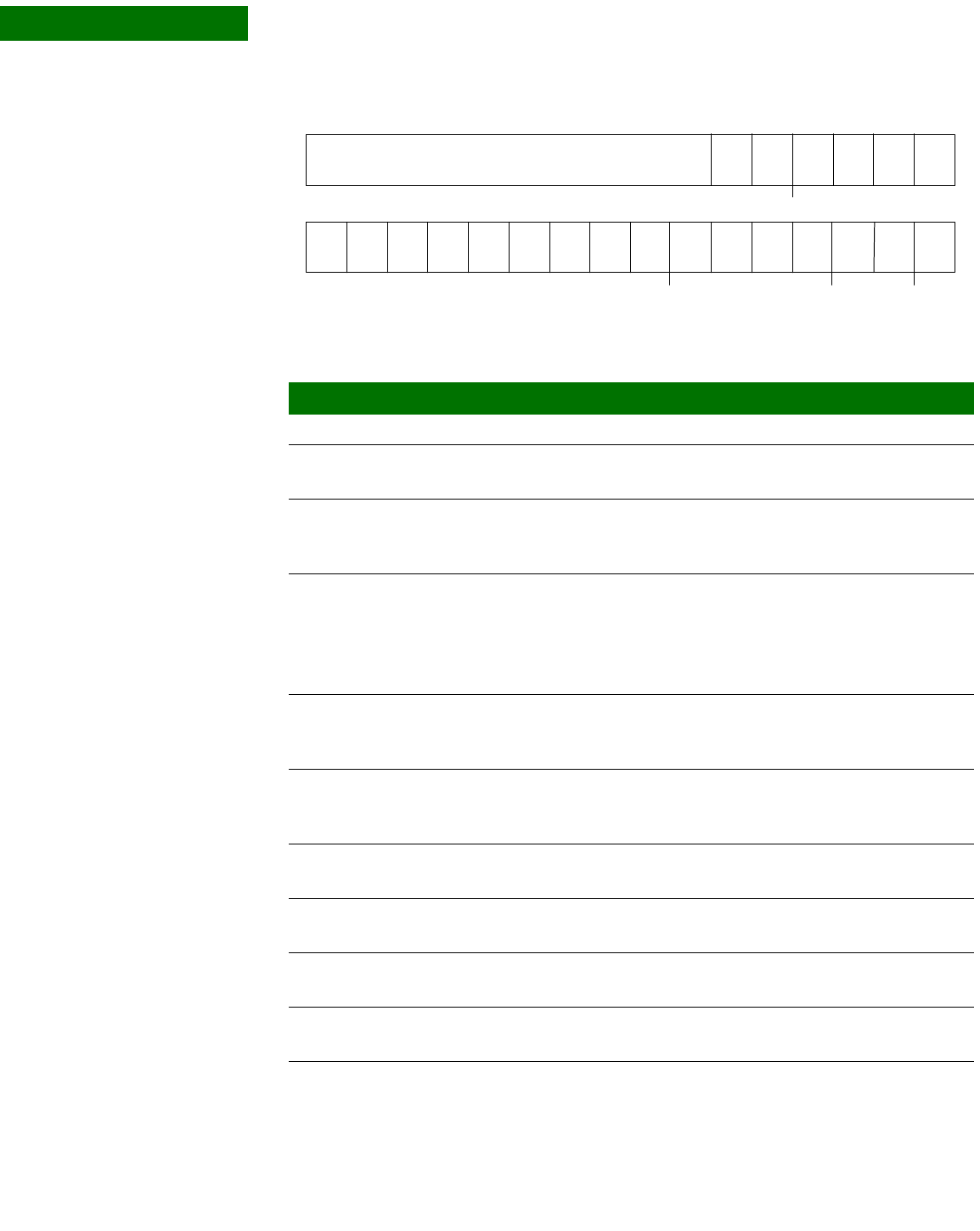

Register

Register bit

assignment

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

MATCH

0

CGAPBGAP

CTS TBC

TX_

IDLE

PARITY

FRA

ME

Not used

BREA

K

MATCH

4

RI

Reser

ved

FORCE OFLOW

RXCLS

MATCH

3

MATCH

2

MATCH

1

DSR DCD RBC

RX_

IDLE

Bits Access Mnemonic Reset Description

D31:22 R/W Not used 0 Write this field to 0.

D21 R/W1TC Reserved 0 UART interrupt

Indicates that the UART has generated an interrupt.

D20 R/W1TC FORCE 0 Force complete

Indicates that a force character transmission operation has

completed.

D19 R/W1TC OFLOW 0 Enable overflow error

Indicates that an overflow occurred in the UART’s 4-

character FIFO.

Note: This should not happen in a properly configured

system.

D18 R/W1TC PARITY 0 Parity error

Indicates that at least one character has been received with

a parity error.

D17 R/W1TC FRAME 0 Frame error

Indicates that at least one character has been received with

a framing error.

D16 R/W1TC BREAK 0 Line break

Indicates that a line break condition has occurred.

D15 R/W1TC BGAP 0 Buffer gap

Indicates that a buffer gap timeout event has occurred.

D14 R/W1TC RXCLS 0 Software receive close

Indicates a software-initiated buffer close has completed.

D13 R/W1TC CGAP 0 Character gap

Indicates that a character gap timeout event has occurred.

D12 R/W1TC MATCH4 0 Character match4

Indicates that a receive character match has occurred

against the Receive Match Register 4.